10-113

10

10.4 TIO (Input/Output-Related 16-Bit Timer)

MULTIJUNCTION TIMERS

32180 Group User’s Manual (Rev.1.0)

WR

Dn

TIOm enable protect

(TIOmPRO)

WR

EN-ON

TIOm external enable

(TIOmEEN or TIOmENS)

TINnS

TIOm count enable

(TIOmCEN)

TIO enable control

Input processing

selection

F/F

F/F

F/F

Event bus

TINn

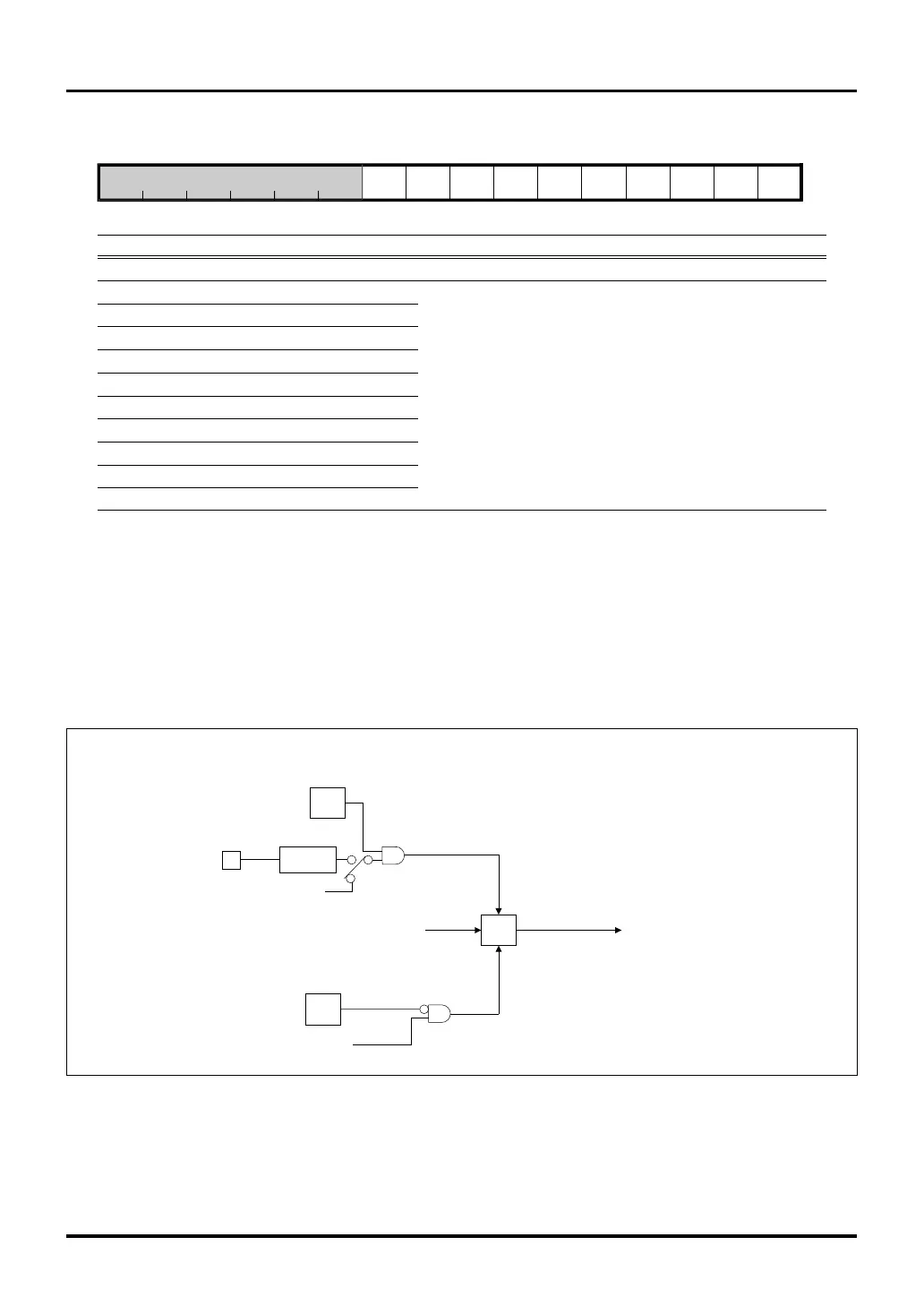

Figure 10.4.5 Configuration of the TIO Enable Circuit

TIO Count Enable Register (TIOCEN) <Address: H’0080 03BE>

b01234567891011121314b15

TIO9CEN TIO8CEN TIO7CEN TIO6CEN TIO5CEN TIO4CEN TIO3CEN TIO2CEN TIO1CEN TIO0CEN

0000000000

<After reset: H’0000>

b Bit Name Function R W

0–5 No function assigned. Fix to "0". 00

6 TIO9CEN (TIO9 count enable bit) 0: Stop count R W

7 TIO8CEN (TIO8 count enable bit) 1: Enable count

8 TIO7CEN (TIO7 count enable bit)

9 TIO6CEN (TIO6 count enable bit)

10 TIO5CEN (TIO5 count enable bit)

11 TIO4CEN (TIO4 count enable bit)

12 TIO3CEN (TIO3 count enable bit)

13 TIO2CEN (TIO2 count enable bit)

14 TIO1CEN (TIO1 count enable bit)

15 TIO0CEN (TIO0 count enable bit)

Note: • This register must always be accessed in halfwords

The TIO Count Enable Register controls operation of the TIO counters. To enable any TIO counter in software,

enable its corresponding enable protect bit for write and set the count enable bit by writing "1". To stop any TIO

counter, enable its corresponding enable protect bit for write and reset the count enable bit by writing "0".

In all but continuous output mode, when the counter stops due to occurrence of an underflow, the count enable

bit is automatically reset to "0". Therefore, the TIO Count Enable Register when accessed for read serves as a

status register indicating whether the counter is operating or idle.

Loading...

Loading...