10

10-180

MULTIJUNCTION TIMERS

10.8 TOU (Output-Related 24-Bit Timer)

32180 Group User’s Manual (Rev.1.0)

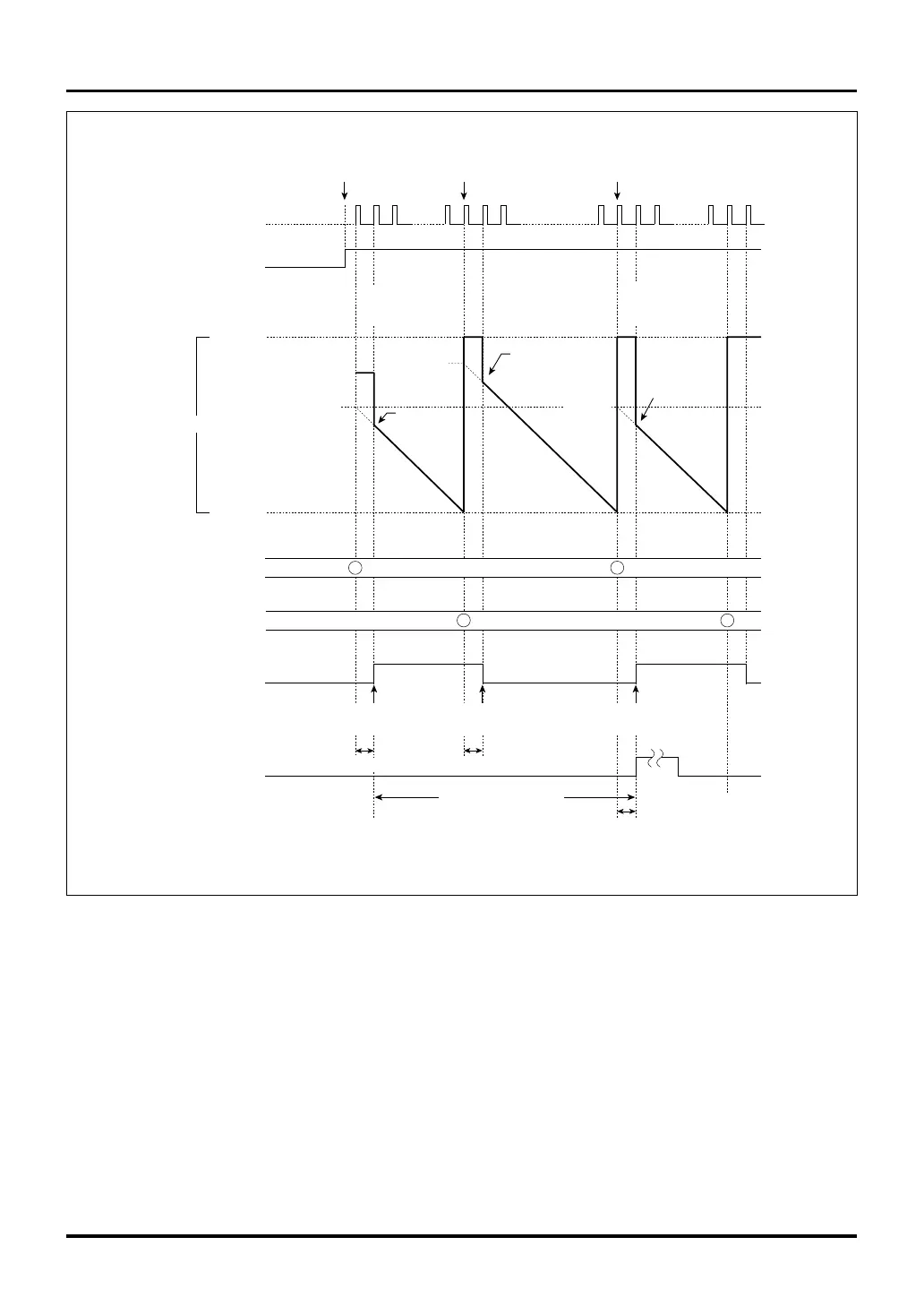

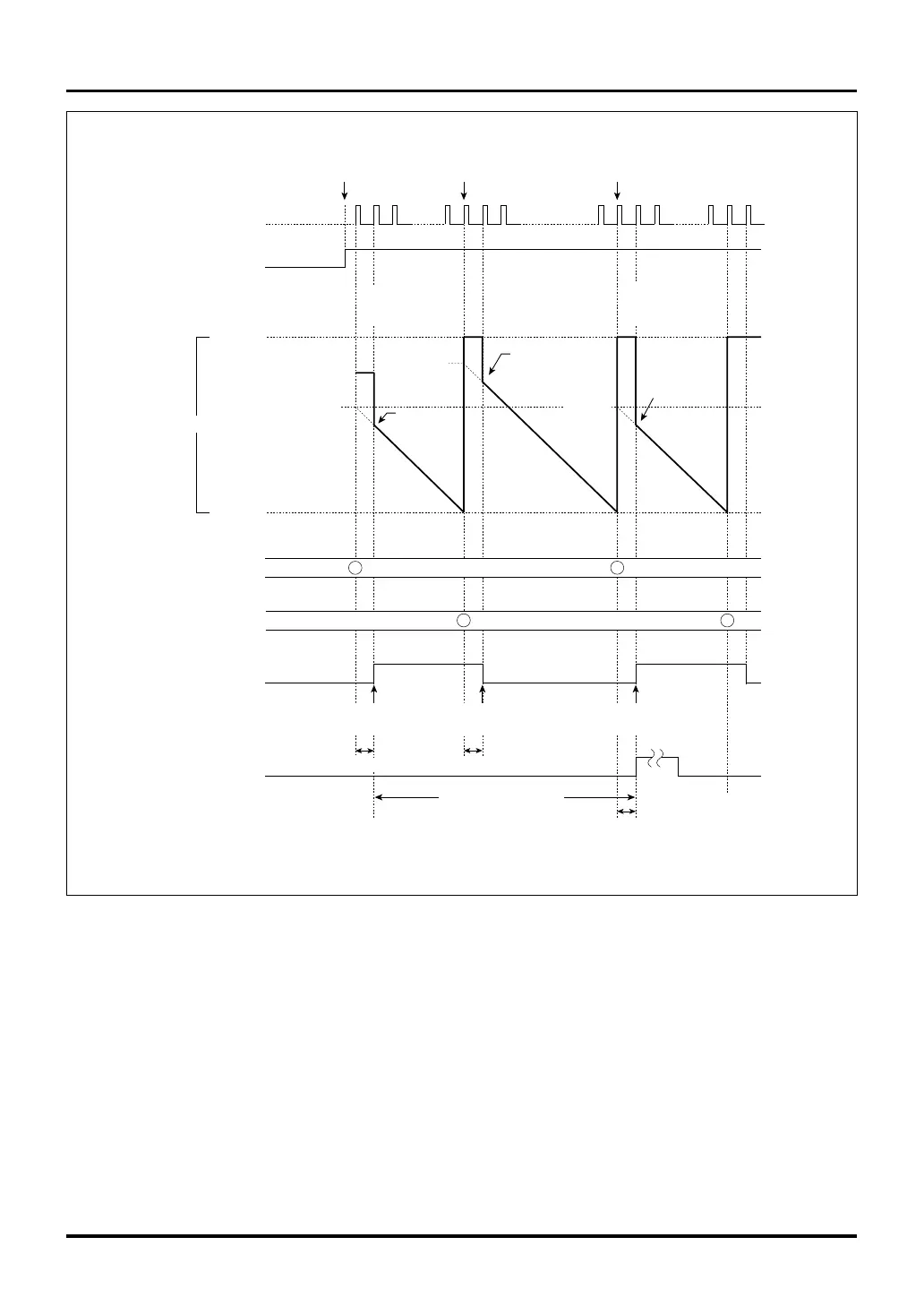

Figure 10.8.9 Typical Operation in PWM Output Mode

Count clock

Counter

H'FFFF

H'0000

Enabled

(by writing to the enable bit

or by external input)

F/F output

Underflow

(first time)

Interrupt request

due to underflow

Enable bit

Note: • This diagram does not show detailed timing information.

Reload 0 register

H'A000

Underflow

(second time)

H'(C000-1)

Data inverted

by underflow

Data inverted

by enable

H'(A000-1)

Data inverted

by underflow

Reload 1 register H'C000

H'A000

PWM output period

H'C000

H'A000

Count down from the

reload 0 register

set value

One count clock equivalent delay

Undefined

value

H'(A000-1)

One count clock equivalent delay

One count clock equivalent delay

Count down from the

reload 1 register

set value

Count down from the

reload 0 register

set value

Loading...

Loading...