10

10-183

MULTIJUNCTION TIMERS

10.8 TOU (Output-Related 24-Bit Timer)

32180 Group User’s Manual (Rev.1.0)

Figure 10.8.12 Reload 0 and Reload 1 Register Updates in PWM Output Mode (For 0% or 100% Duty-Cycle Wave Output)

H'0001 H'FFFF

H'1000

FFFF

H'2000

FFFF

H'9000

H'1000

H'2000

FFFF

H'9000

8FFFH'0000

H'2000

H'9000

H'0001 H'FFFF

H'1000

H'0FFF

H'2000

FFFF

H'9000

H'1000

H'2000

FFFF

H'9000

H'0FFEH'0000

H'2000 H'9000

(a) When reload register updates take effect in the current period (reflected in the next period)

Count clock

Reload 0 register

Reload 1 register

Counter

Interrupt due

to underflow

Timing at which reload 0 and reload 1

registers are updated

New PWM output period

Operation by new reload value written

Reload 0 register

Reload 1 register

F/F output

Write to reload 1

Write to reload 0

(Reload 1 data latched)

Enlarged

view

New PWM

output period

Old PWM output period

F/F output

PWM period latched

Reload 1 buffer

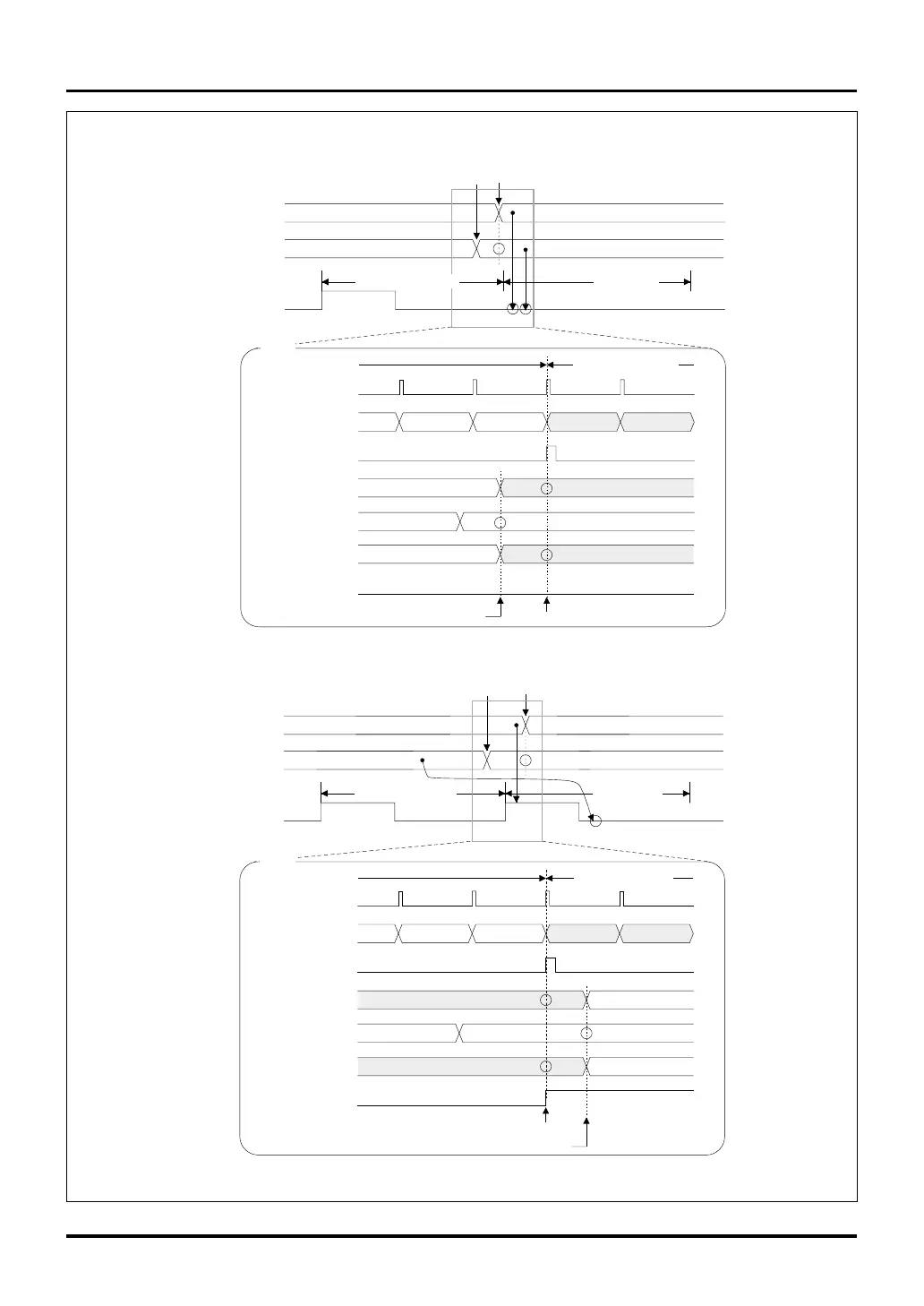

(b) When reload register updates take effect in the next period (reflected one period later)

Old PWM output period

Operation by old reload value

Old PWM

output period

Note: • This diagram does not show detailed timing information.

Count clock

Reload 0 register

Reload 1 register

Counter

Interrupt due

to underflow

Timing at which reload 0 and reload 1

registers are updated

Reload 0 register

Reload 1 register

F/F output

Write to reload 1

Write to reload 0

(Reload 1 data latched)

Enlarged

view

Old PWM output period

F/F output

PWM period latched

Reload 1 buffer

Loading...

Loading...