11

11-3

A-D Converters

32180 Group User's Manual (Rev.1.0)

11.1 Outline of A-D Converters

(8) Interrupt and DMA Transfer Request Generation Function

An A-D conversion interrupt or DMA transfer request can be generated each time A-D conversion or comparate

operation in single mode is completed, as well as when a single-shot scan operation or one cycle of continuous

scan operation is completed.

Note 1: To discriminate between the comparison performed internally by the successive approximation-

type A-D Converter and that performed in comparator mode using the same A-D Converter as a

comparator, the comparison in comparator mode is referred to in this manual as “comparate.”

Table 11.1.1 outlines the A-D Converters. Figures 11.1.1 and 11.1.2 show block diagrams of A-D Converters, respectively.

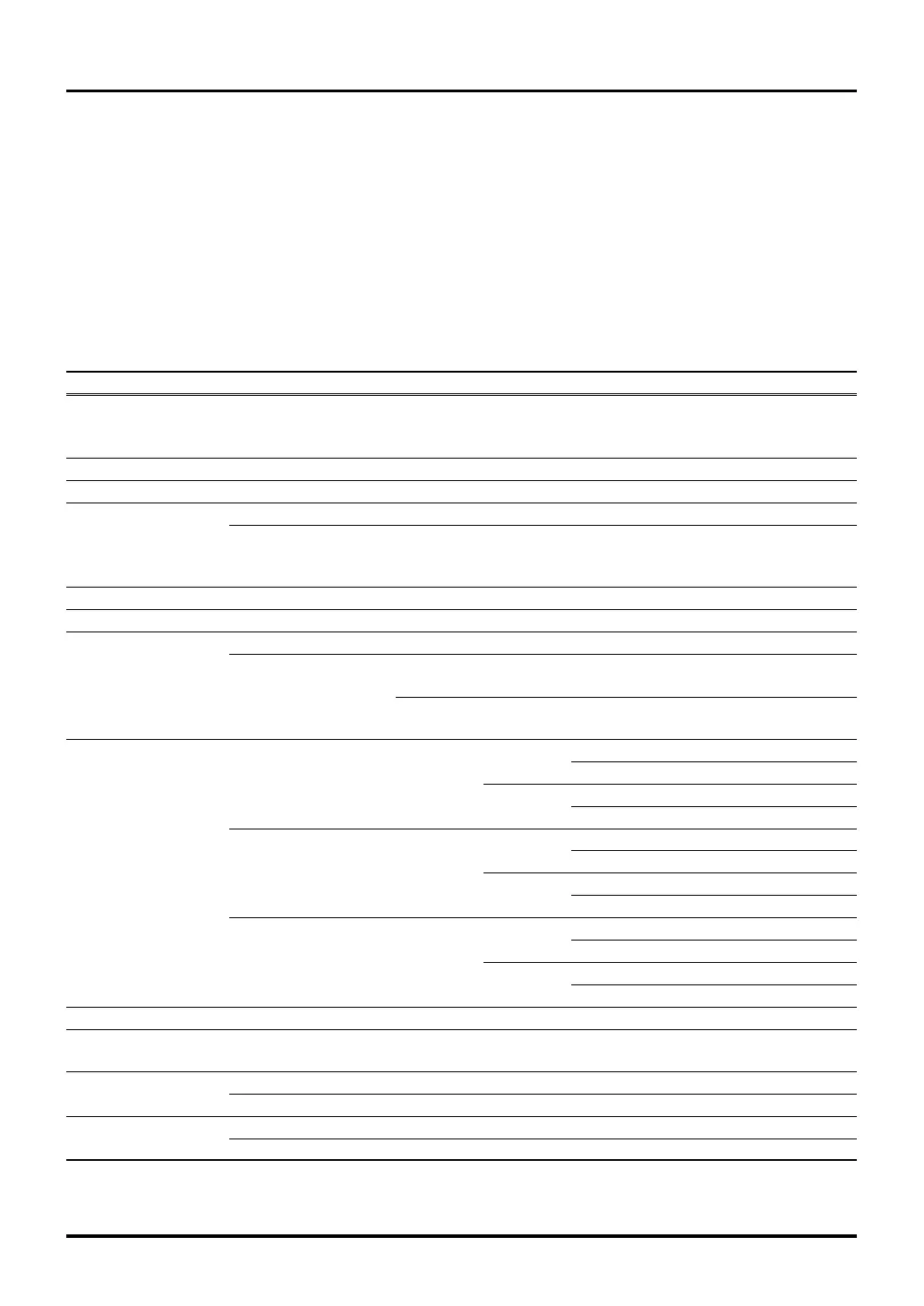

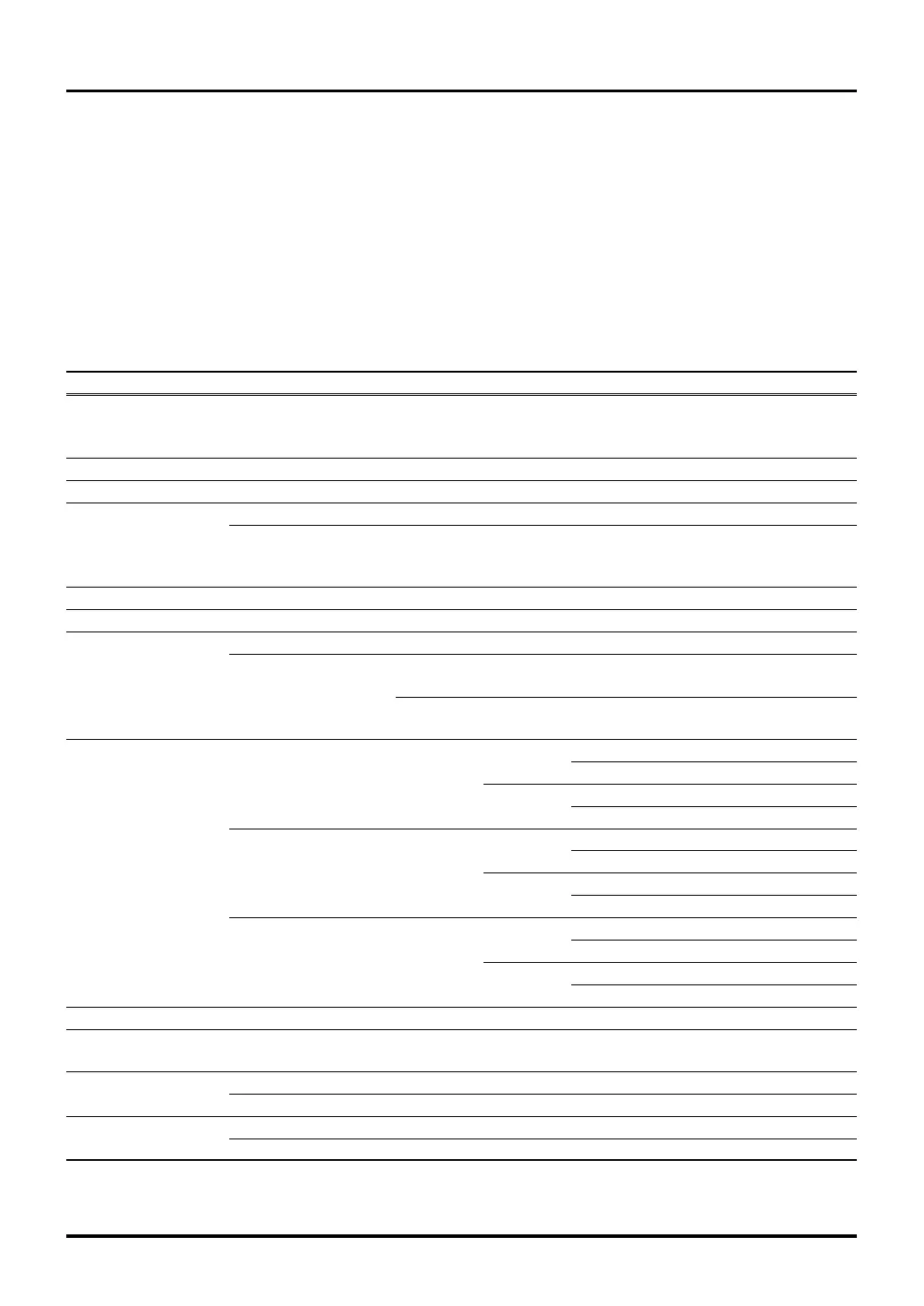

Table 11.1.1 Outline of the A-D Converters

Item Description

Analog input 16 channels ×2

A-D0 Converter: 16-channel analog input-only pins

A-D1 Converter: 16-channel analog input-only pins

A-D conversion method Successive approximation method

Resolution 10 bits (Conversion result can be read out in either 8 or 10 bits)

Absolute accuracy (Note 1) During slow mode: ±2 SLB at normal speed, ±2 SLB at double speed

Conditions: Ta = 25°C, During fast mode: ±3 SLB at normal speed, ±3 SLB at double speed

AVCC0, 1 = 5.12 V, Note: • The accuracy when sample-and-hold is enabled is T.B.D.

VREF0, 1 = 5.12 V

Conversion mode A-D conversion mode and comparator mode

Operation mode Single mode, single-shot scan mode and continuous scan mode

Conversion start trigger Software start Started by setting the A-D conversion start bit to "1"

Hardware start A-D0 Converter MJT (input event bus 2), MJT (input event bus 3),

MJT (output event bus 3) and MJT (TIN23S)

A-D1 Converter MJT (input event bus 2), MJT (input event bus 3),

TID1_udf/ovf and MJT (TIN23S)

Conversion speed During single mode Slow mode Normal speed 299BCLK 14.95µs (Note 2)

BCLK: (• When sample-and-hold disabled Double speed 173BCLK 8.65µs

Internal peripheral clock

• When normal sample-and-hold enabled) Fast mode Normal speed 131BCLK 6.55µs

Double speed 89BCLK 4.45µs

During single mode Slow mode Normal speed 191BCLK 9.55µs

(When fast sample-and-hold enabled) Double speed 101BCLK 5.05µs

Fast mode Normal speed 95BCLK 4.75µs

Double speed 53BCLK 2.65µs

During comparator mode Slow mode Normal speed 47BCLK 2.35µs

Double speed 29BCLK 1.45µs

Fast mode Normal speed 23BCLK 1.15µs

Double speed 17BCLK 0.85µs

Sample-and-hold function Sample-and-hold function can be enabled or disabled as necessary.

A-D disconnection Influences of the analog input voltage wrapping around from any preceding channel during scan

detection assist function mode operation are suppressed.

Interrupt request Generated when A-D conversion or comparate operation is completed

generation function Generated when a single-shot scan operation or one cycle of continuous scan operation is completed

DMA transfer request Generated when A-D conversion or comparate operation is completed

generation function Generated when a single-shot scan operation or one cycle of continuous scan operation is completed

Note 1: The conversion accuracy stipulated here refers to that of the microcomputer alone, with influences of the power

supply wiring and noise on the board not taken into account.

Note 2: This indicates the conversion time when f(BCLK) = 20 MHz (1 BCLK = 50 ns).

Loading...

Loading...