2

2-13

32180 Group User’s Manual (Rev.1.0)

CPU

2.6 Data Formats

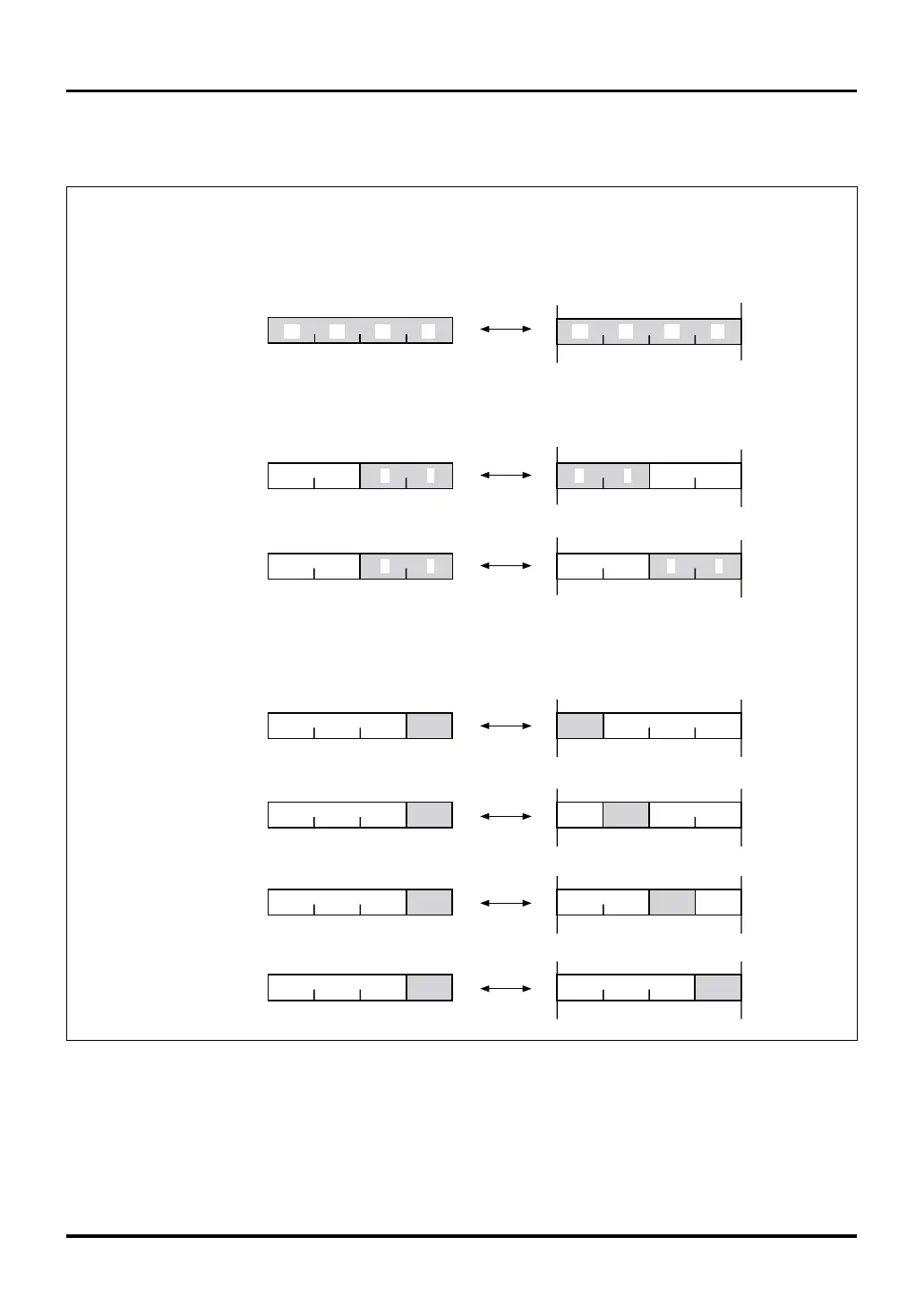

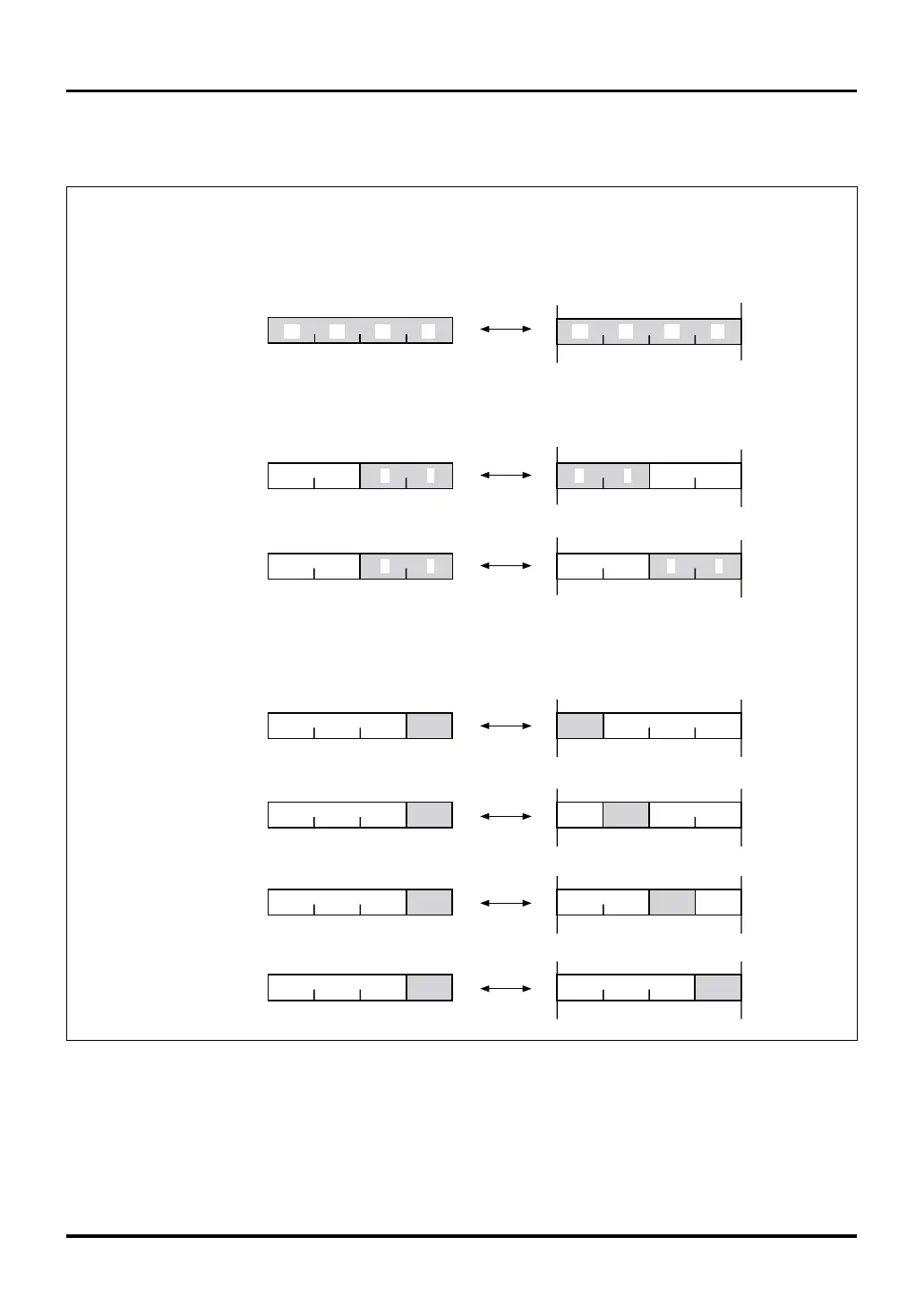

(7) Notes on data transfer

When transferring data, be aware that data arrangements in registers and memory are different.

• Word data (32 bits)

+0 +1 +2 +3

b0 b31

HH HL LH LL

b0 b31

HH HL LH LL

• Halfword data (16 bits)

+0 +1 +2 +3

b0 b31

H L

b0 b15

H L

• Byte data (8 bits)

+0 +1 +2 +3

b0

b31 b0 b7

(R0–R15)

(R0–R15)

(R0–R15)

+0 +1 +2 +3

b0

b31 b8 b15

(R0–R15)

+0 +1 +2 +3

b0

b31 b16 b23

(R0–R15)

+0 +1 +2 +3

b0

b31 b24 b31

(R0–R15)

+0 +1 +2 +3

b0 b31

H L

b16 b31

H L

(R0–R15)

Data in registers Data in memory

Figure 2.6.9 Difference in Data Arrangements

Loading...

Loading...