12

12-9

Serial I/O

12.2 Serial I/O Related Registers

32180 Group User's Manual (Rev.1.0)

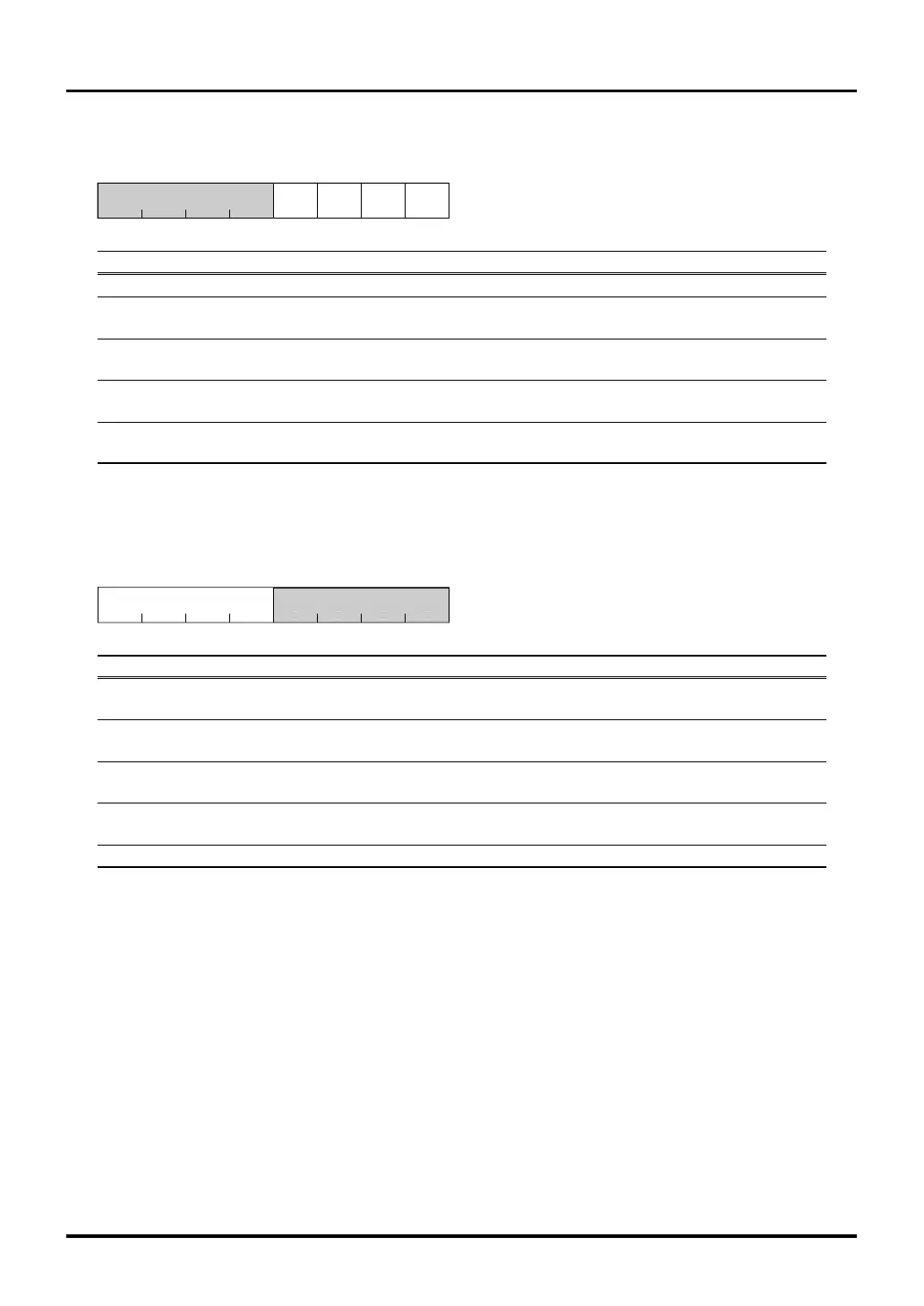

SIO23 Interrupt Request Status Register (SI23STAT) <Address: H’0080 0100>

123456b7b0

IRQT2 IRQR3IRQT3IRQR2

0000

<After reset: H’00>

b Bit Name Function R W

0–3 No function assigned. Fix to "0". 00

4 IRQT2 0: Interrupt not requested R (Note 1)

SIO2 transmit interrupt request status bit 1: Interrupt requested

5 IRQR2 0: Interrupt not requested R (Note 1)

SIO2 receive interrupt request status bit 1: Interrupt requested

6 IRQT3 0: Interrupt not requested R (Note 1)

SIO3 transmit interrupt request status bit 1: Interrupt requested

7 IRQR3 0: Interrupt not requested R (Note 1)

SIO3 receive interrupt request status bit 1: Interrupt requested

Note 1: Only writing "0" is effective. Writing "1" has no effect; the bit retains the value it had before the write.

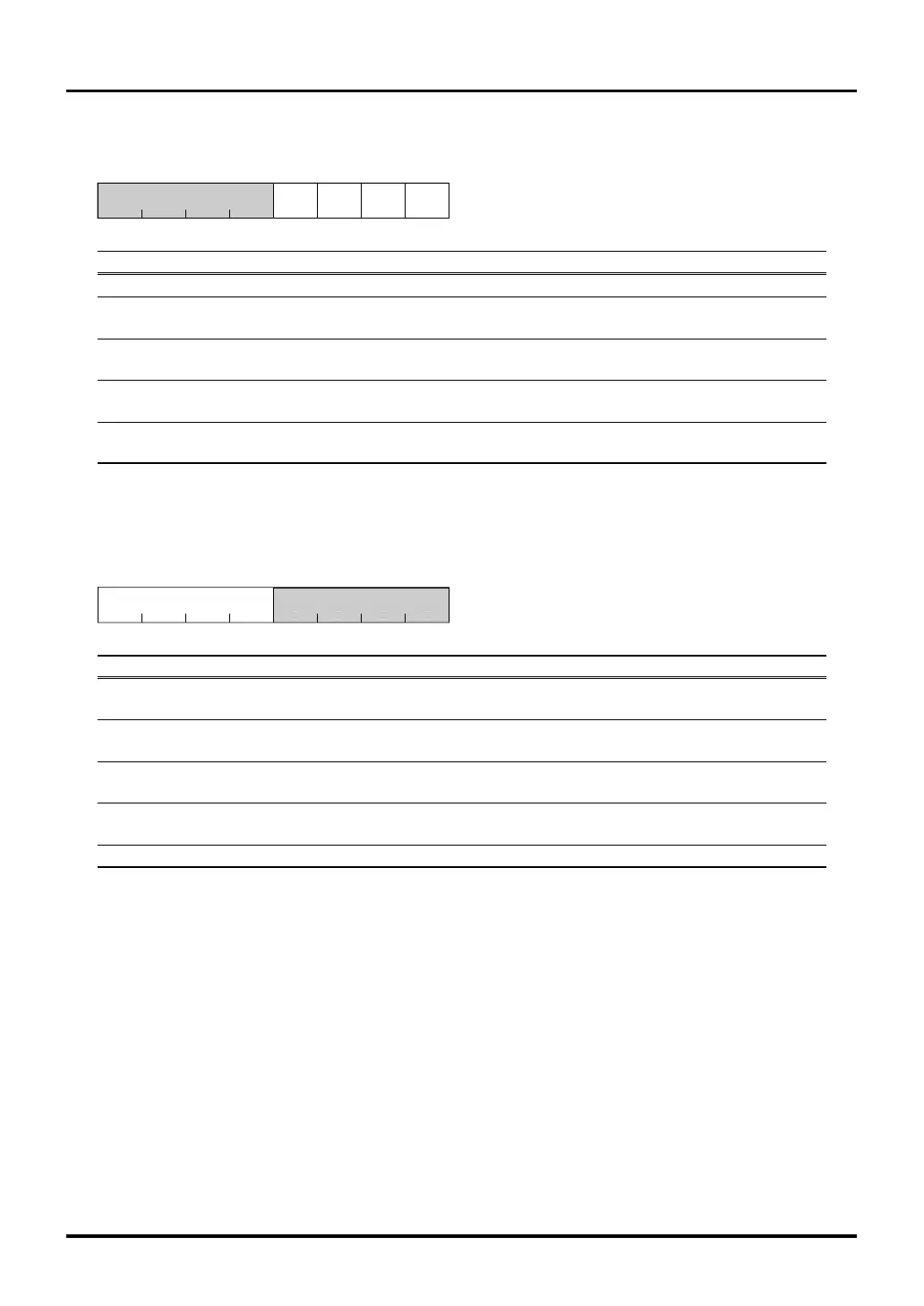

SIO45 Interrupt Request Status Register (SI45STAT) <Address: H’0080 0A00>

123456b7b0

IRQT4 IRQR5IRQT5IRQR4

0000

<After reset: H’00>

b Bit Name Function R W

0 IRQT4 0: Interrupt not requested R (Note 1)

SIO4 transmit interrupt request status bit 1: Interrupt requested

1 IRQR4 0: Interrupt not requested R (Note 1)

SIO4 receive interrupt request status bit 1: Interrupt requested

2 IRQT5 0: Interrupt not requested R (Note 1)

SIO5 transmit interrupt request status bit 1: Interrupt requested

3 IRQR5 0: Interrupt not requested R (Note 1)

SIO5 receive interrupt request status bit 1: Interrupt requested

4–7 No function assigned. Fix to "0". 00

Note 1: Only writing "0" is effective. Writing "1" has no effect; the bit retains the value it had before the write.

These registers indicate the transmit/receive interrupt requests from each SIO.

[Setting the interrupt request status bit]

This bit can only be set in hardware, and cannot be set in software.

[Clearing the interrupt request status bit]

This bit is cleared by writing "0" in software.

Note: • If the status bit is set in hardware at the same time it is cleared in software, the former has

priority and the status bit is set.

When writing to the SIO Interrupt Request Status Register, make sure only the bits to be cleared are set to "0"

and all other bits are set to "1". Those bits that have been set to "1" are unaffected by writing in software and

retain the value they had before the write.

Loading...

Loading...