13-23

13

32180 Group User’s Manual (Rev.1.0)

13.2 CAN Module Related Registers

CAN MODULE

(1) SJW bits (Bits 0–1)

These bits set the reSynchronization Jump Width.

(2) PH2 bits (Bits 2–4)

These bits set the width of Phase Segment2.

(3) PH1 bits (Bits 5–7)

These bits set the width of Phase Segment1.

(4) PRB bits (Bits 8–10)

These bits set the width of Propagation Segment.

(5) SAM bit (Bit 11)

This bit sets the number of times each bit is sampled. When SAM = "0", the value sampled at the end of

Phase Segment1 is assumed to be the value of the bit. When SAM = "1", the value of the bit is determined by

a majority circuit from three sampled values, each sampled 2 Tq’s before, 1 Tq before, and at the end of

Phase Segment1.

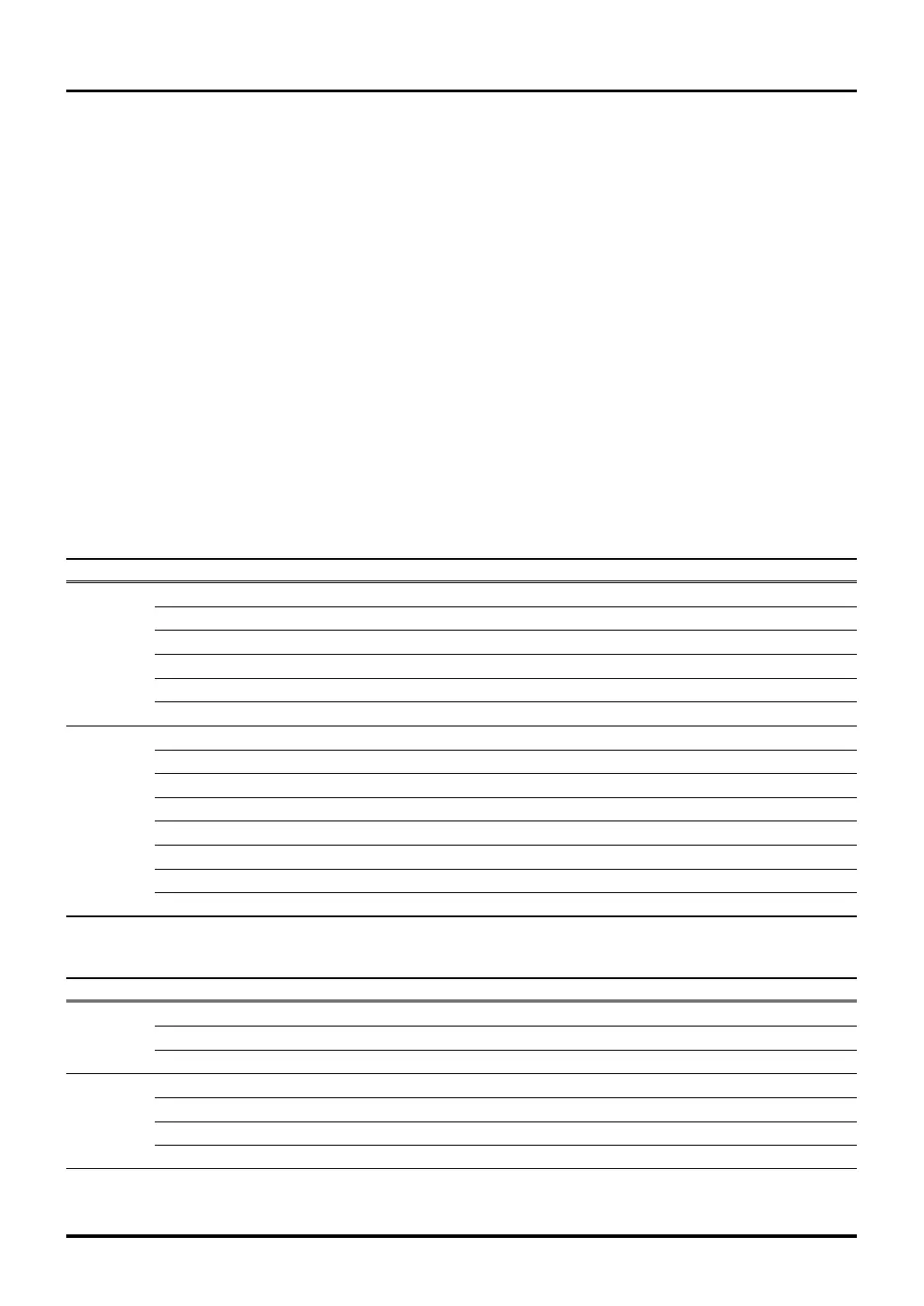

Table 13.2.1 Typical Settings of Bit Timing when CPU Clock = 80 MHz

Baud Rate BRP Set Value Tq Period (ns) No. of Tq’s in 1 Bit PROP + PH1 PH2 Sampling Point

1M bps 1 50 20 13 6 70%

3 100 10 7 2 80%

3 100 10 6 3 70%

3 100 10 5 4 60%

4 125 8 5 2 75%

4 125 8 4 3 63%

500K bps 4 125 16 13 2 88%

4 125 16 12 3 81%

4 125 16 11 4 75%

7 200 10 7 2 80%

7 200 10 6 3 70%

7 200 10 5 4 60%

9 250 8 5 2 75%

9 250 8 4 3 63%

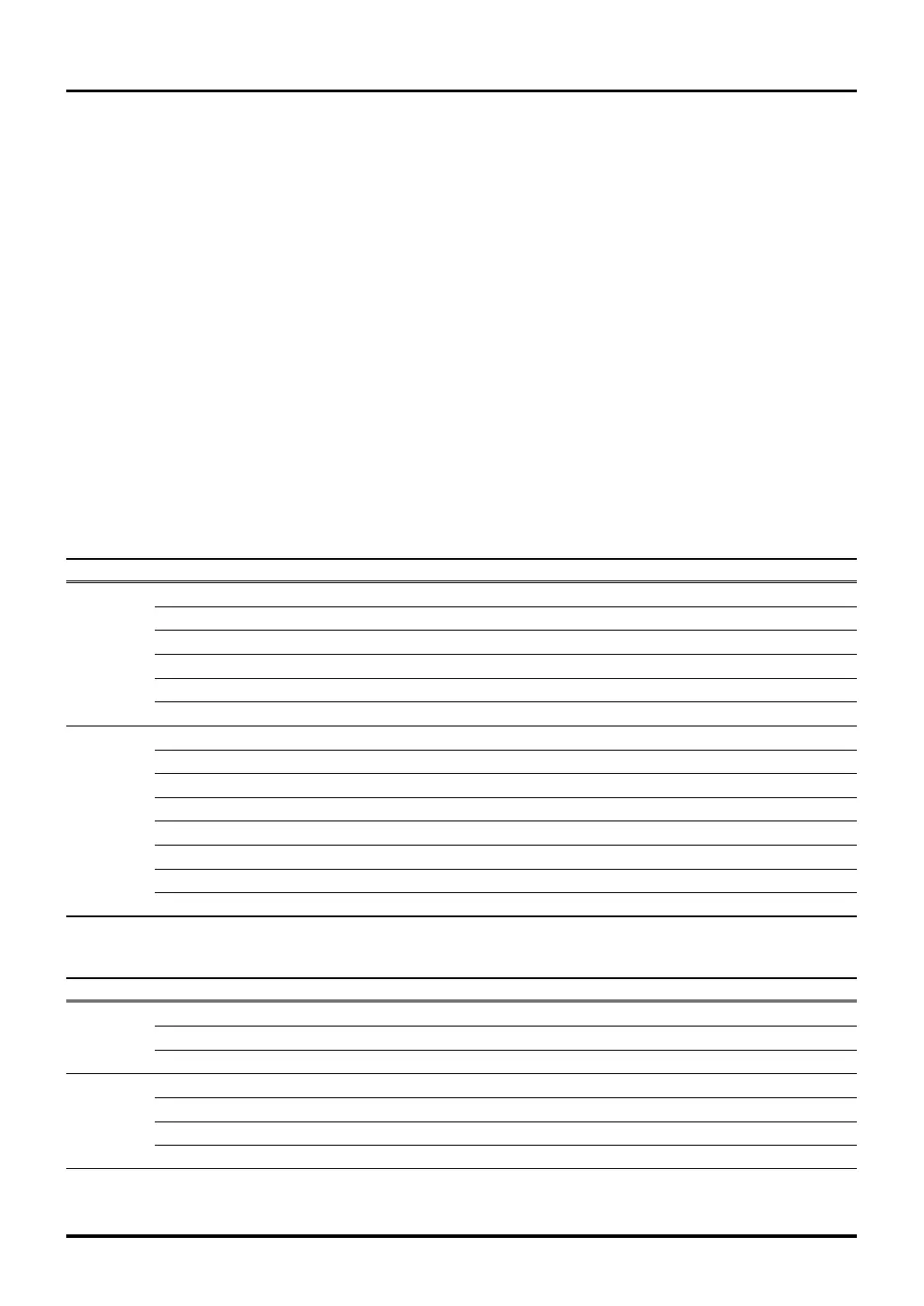

Table 13.2.2 Typical Settings of Bit Timing when CPU Clock = 64 MHz

Baud Rate BRP Set Value Tq Period (ns) No. of Tq’s in 1 Bit PROP + PH1 PH2 Sampling Point

1M bps 1 62.5 16 10 5 69%

3 125 8 5 2 75%

3 125 8 4 3 63%

500K bps 3 125 16 13 2 88%

3 125 16 11 4 75%

7 250 8 5 2 75%

7 250 8 4 3 63%

Loading...

Loading...