16

16-17

WAIT CONTROLLER

16.3 Typical Operation of the Wait Controller

32180 Group User’s Manual (Rev.1.0)

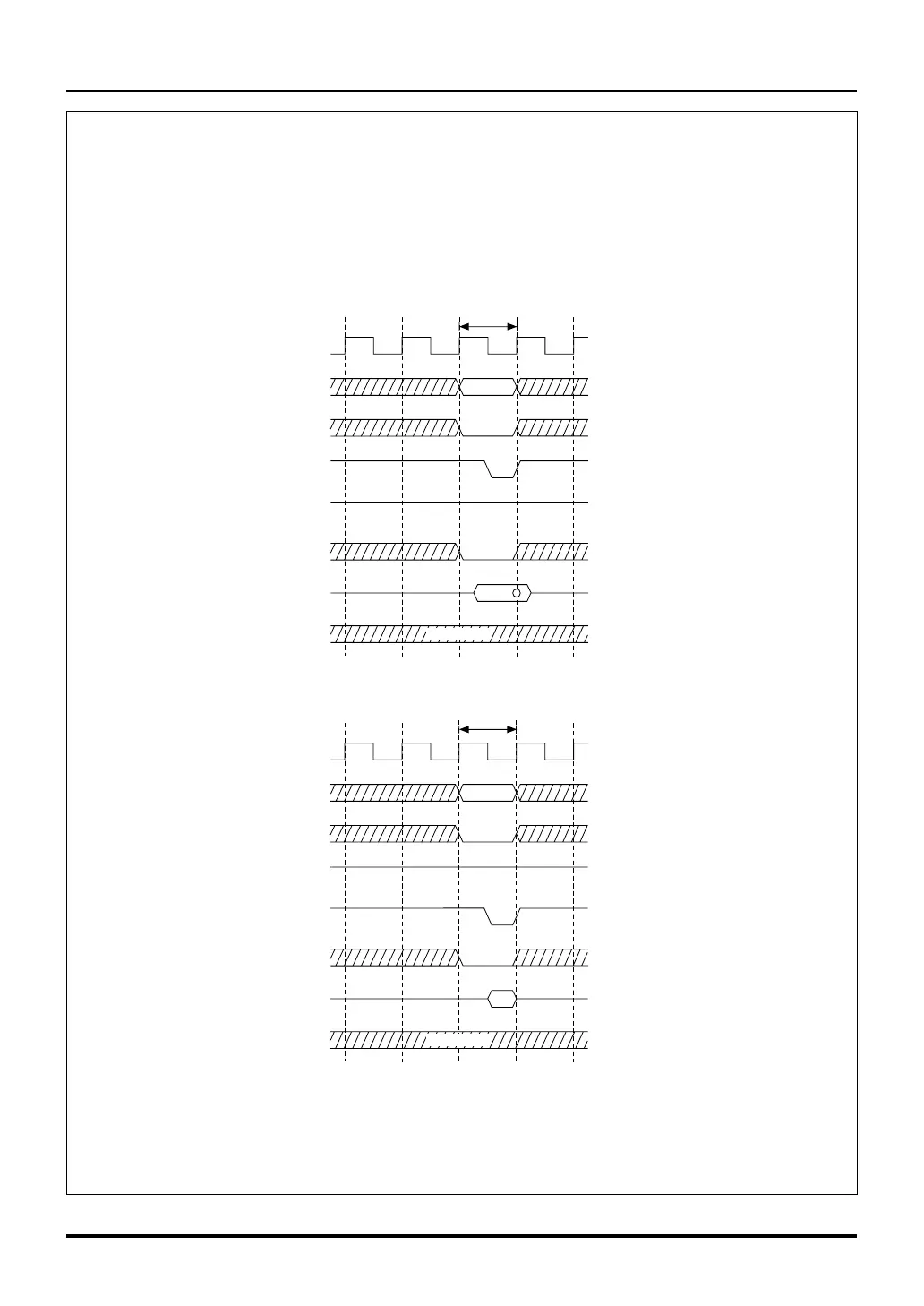

Figure 16.3.12 Read/Write Timing (for Zero Wait Access)

Read

Read

(1 cycle)

BCLK

A11–A30

CS0#–CS3#

WR#

DB0–DB15

WAIT#

RD#

"H"

Note 1: For details about the Bus Mode Control Register, see Section 15.2.3, "Bus Mode Control Register."

Note 2: For details about the CS Area Wait Control Register, see Section 16.2.1, "CS Area Wait Control Registers."

Notes: • Circles in the above diagram indicate the sampling timing.

• When zero wait state is selected, wait states inserted by WAIT# are not accepted.

(Don't Care)

BHE#, BLE#

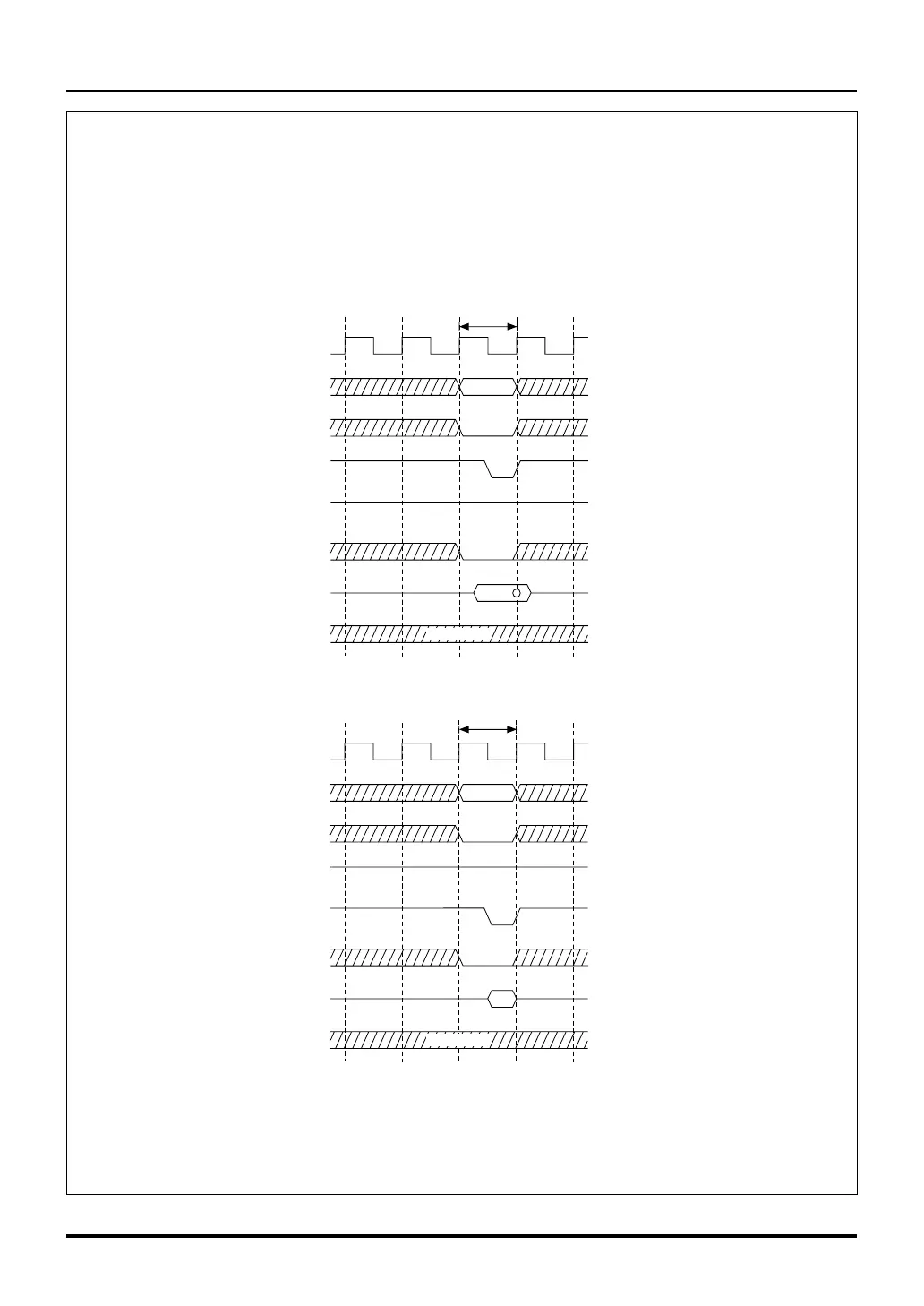

Write

Write

(1 cycle)

BCLK

A11–A30

CS0#–CS3#

WR#

DB0–DB15

WAIT#

RD#

"H"

(Don't Care)

BHE#, BLE#

Bus Mode Control Register (Note 1)

BUSMOD bit = 1 (byte enable separated)

CS Area Wait Control Register (Note 2)

WTCSEL bit = 000 (zero wait)

SWAIT bit = 0 (without strobe wait)

RECOV bit = 0 (without recovery cycle)

IDLE bit = 0 (without idle cycle)

Loading...

Loading...