21

21-45

ELECTRICAL CHARACTERISTICS

32180 Group User's Manual (Rev.1.0)

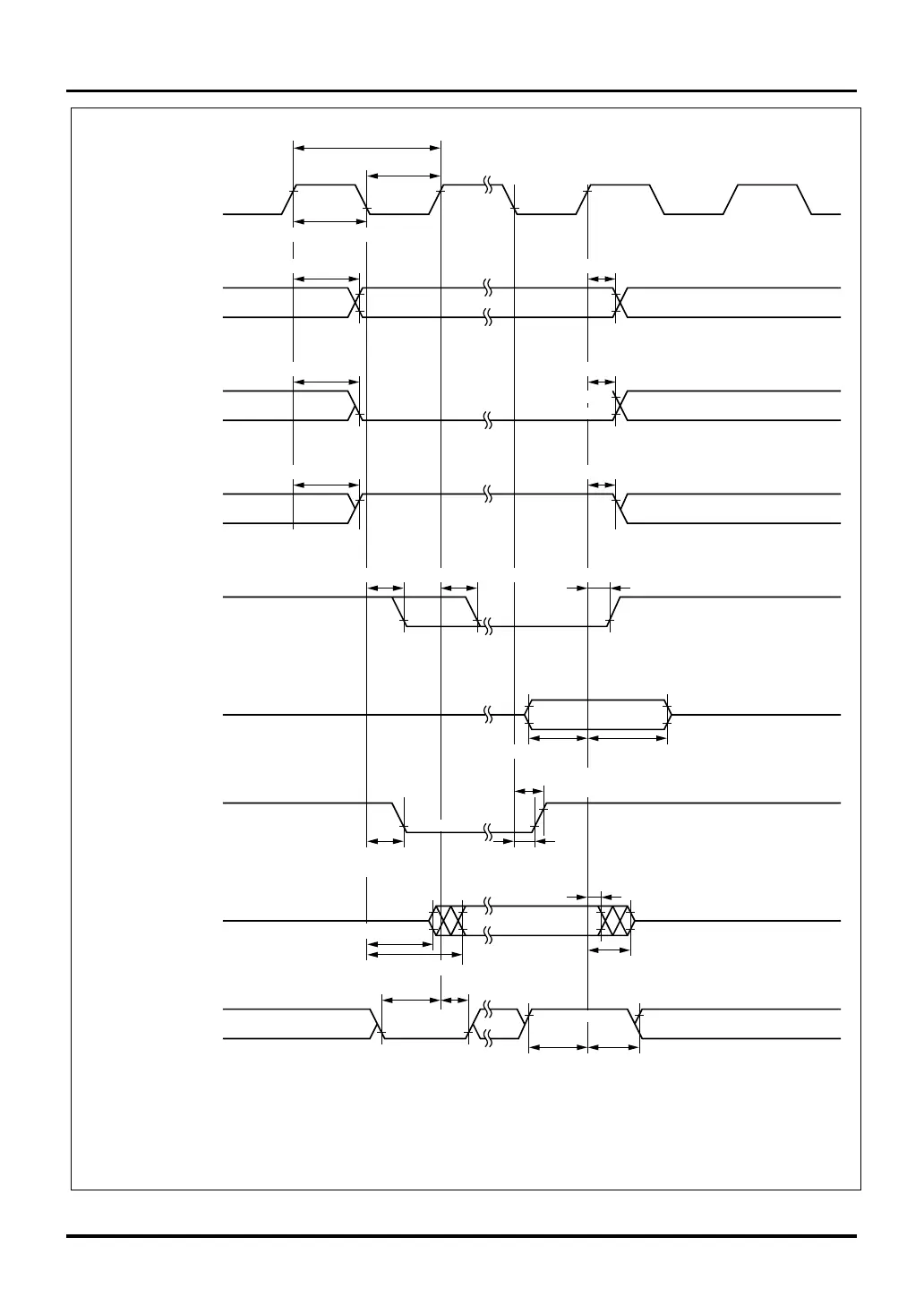

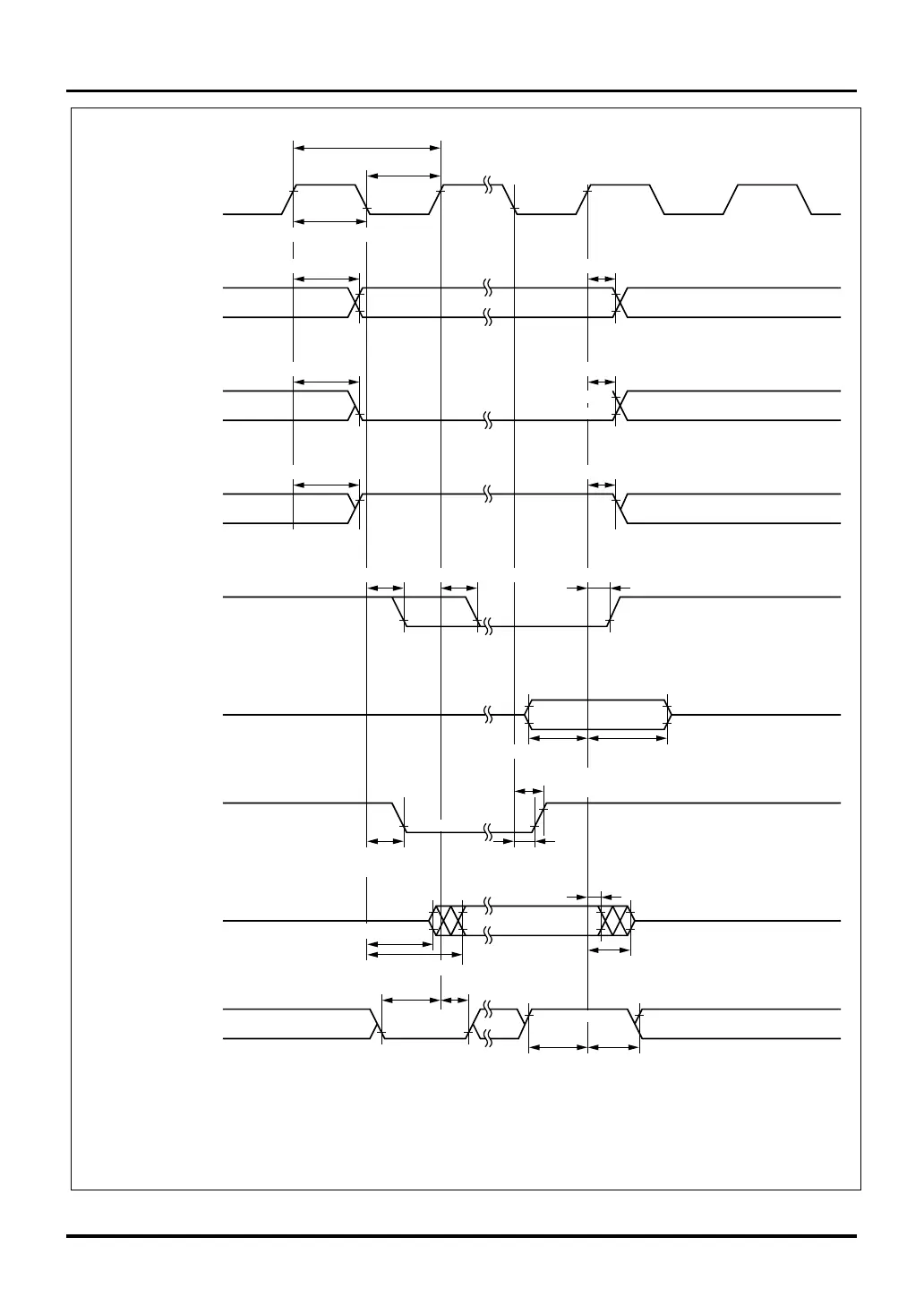

Figure 21.8.6 Read and Write Timing (Relative to BCLK) with 1 or More Wait States

Notes: • For signal-to-signal timing, see Figure 21.8.8, "Read Timing (Relative to Read Pulse),"

and Figure 21.8.9, "Write Timing (Relative to Write Pulse)."

• When using the threshold switching function, the data input and WAIT# voltage levels are determined

with respect to the rated minimum and maximum values for VIH and VIL.

BCLK

[16]

tc(BCLK)

Data output

(DB0–DB15)

Address

(A11–A30)

BLW#

BHW#

CS#

(Access area)

WAIT#

0.43VCC-BUS

0.16VCC-BUS

[19]

td(BCLKH-A)

0.43VCC-BUS

[17]

tw(BCLKH)

[21]

tv(BCLKH-A)

[18]

tw(BCLKL)

[20]

td(BCLKH-CS)

[22]

tv(BCLKH-CS)

[22]

tv(BCLKH-CS)

[24]

tv(BCLKH-RDL)

[92]

td(BCLKH-RDL)

0.16VCC-BUS

0.43VCC-BUS

0.16VCC-BUS

[23]

td(BCLKL-RDL)

[20]

td(BCLKH-CS)

0.43VCC-BUS

0.16VCC-BUS

[32]

th(BCLKH-D)

[31]

tsu(D-BCLKH)

[26]

tv(BCLKL-BLWL)

tv(BCLKL-BHWL)

[28]

tv(BCLKH-D)

[30]

tpxz(BCLKH-DZ)

[29]

tpzx(BCLKL-DZ)

[27]

td(BCLKL-D)

[33]

tsu(WAITL-BCLKH)

[34]

th(BCLKH-WAITL)

[79]

th(BCLKH-WAITH)

[78]

tsu(WAITH-BCLKH)

[25]

td(BCLKL-BLWL)

td(BCLKL-BHWL)

0.16VCC-BUS

0.43VCC-BUS

0.16VCC-BUS

0.43VCC-BUS

0.16VCC-BUS

0.16VCC-BUS

0.43VCC-BUS

CS#

(Non-access area)

RD#

Data input

(DB0–DB15)

[97]

td(BCLKL-BLWH)

td(BCLKL-BHWH)

21.8 A.C. Characteristics (when VCCE = 3.3 V)

Loading...

Loading...