Appendix 2

Appendix 2-2

32180 Group User's Manual (Rev. 1.0)

INSTRUCTION PROCESSING TIME

Appendix 2.1 32180 Instruction Processing Time

Appendix 2.1 32180 Instruction Processing Time

For microcomputers, the number of instruction execution cycles in the E stage (Note 1) normally represents their

instruction processing time. However, depending on pipeline operation, other stages may affect the instruction

processing time. Especially when a branch instruction is executed, the processing time in each of the IF (Instruc-

tion Fetch), D (Decode) and E (Execution) stages of the next instruction must be taken into account.

The tables below show the instruction processing time in each pipelined stage of the 32180.

Note 1: Two E stages, E1 and EM, are used for the FPU instructions.

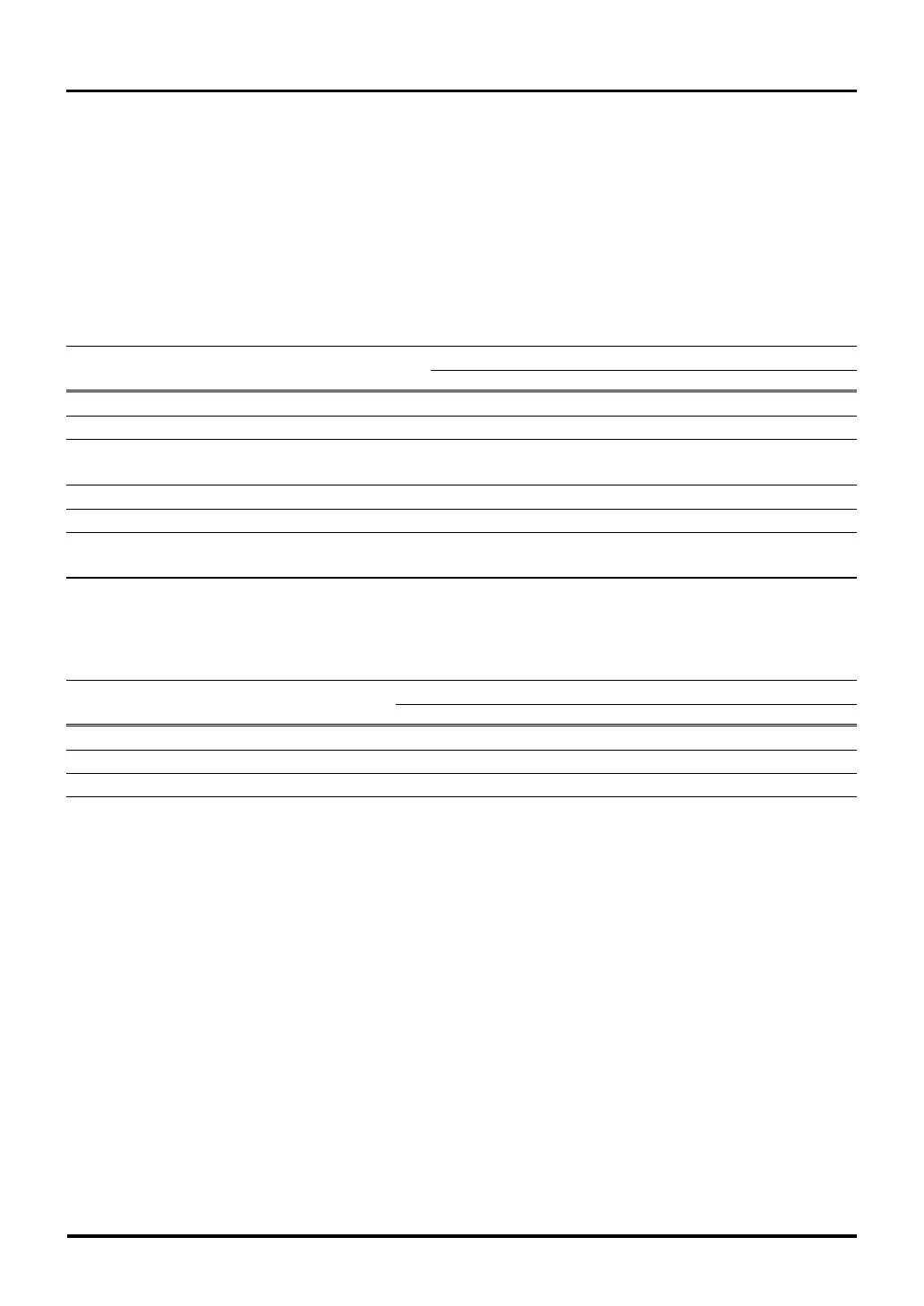

Table 2.1.1 Instruction Processing Time in Each Pipelined Stage (Other Than FPU Instructions)

Number of Execution Cycles in Each Stage

Instruction IF D E MEM1 MEM2 WB

Load instructions (LD, LDB, LDUB, LDH, LDUH, LOCK) R(Note 1) 1 1 R(Note 1) 1 1

Store instructions (ST, STB, STH, UNLOCK) R(Note 1) 1 1 W(Note 1) 1 (1)(Note 2)

BSET and BCLR instructions R(Note 1) 1 R(Note 1)W(Note 1) 1 –

+3

Multiply instructions (MUL) R(Note 1) 1 3 – – 1

Divide/remainder instructions (DIV, DIVU, REM, REMU) R(Note 1) 1 37 – – 1

Other instructions(including DSP function instructions R(Note 1) 1 1 – – 1

BTST, SETPSW and CLRPSW)

Note 1: See the calculation methods for R and W described in the next page.

Note 2: Of the store instructions, only those that have register indirect + register update addressing modes require one cycle

in the WB stage (but not more than that).

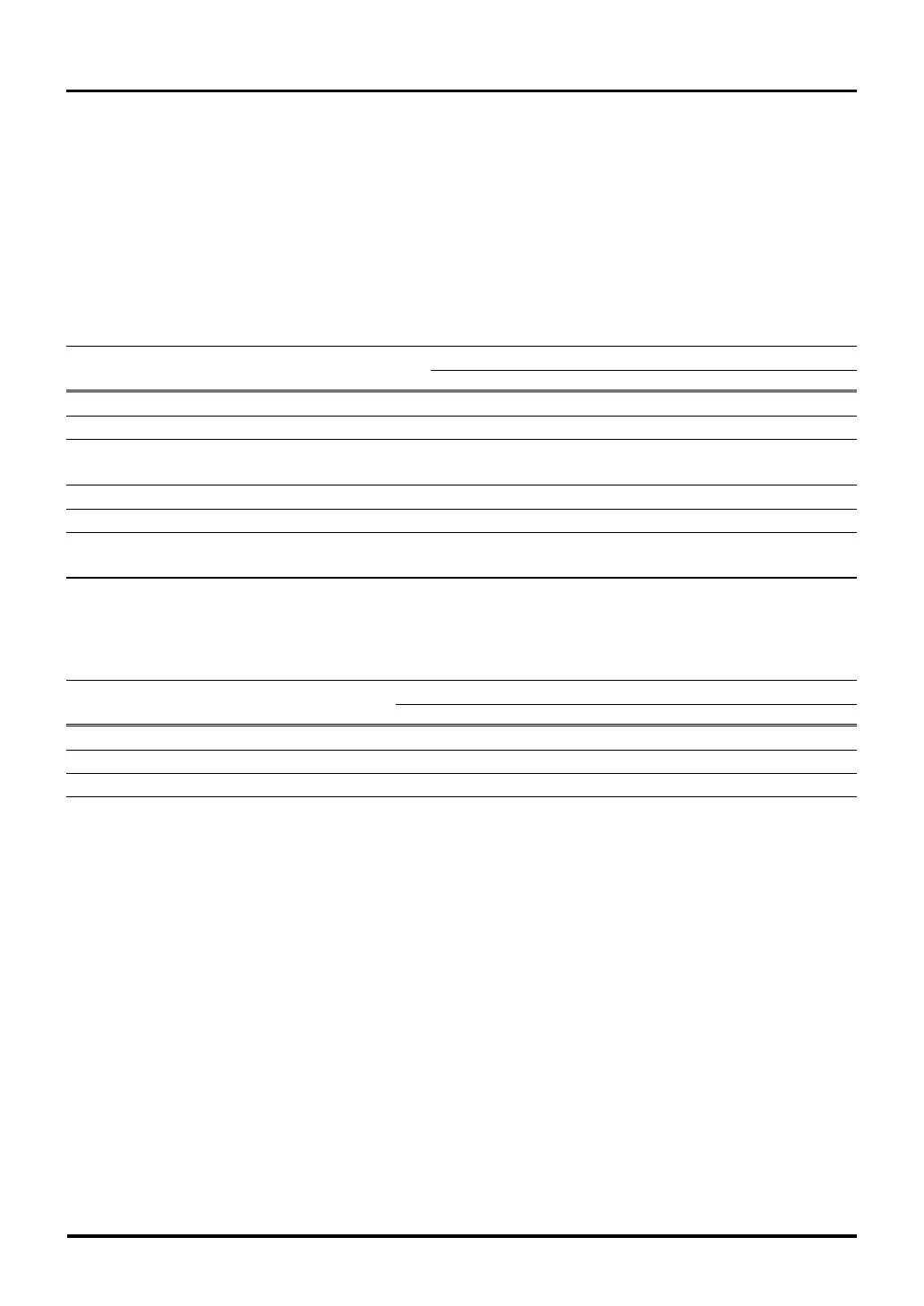

Table 2.1.2 Instruction Processing Time in Each Pipelined Stage (FPU Instructions)

Number of Execution Cycles in Each Stage

Instruction IF D E1 EM EA E2 WB

FMADD and FMSUB instructions R(Note 1) 1 – 1 1 1 1

FDIV instruction R(Note 1) 1 14 – – 1 1

Other FPU instructions R(Note 1) 1 1 – – 1 1

Note 1: See the calculation methods for R and W described in the next page.

Loading...

Loading...