Debug in Depth

ARM DDI 0210C Copyright © 2001, 2004 ARM Limited. All rights reserved. B-51

B.15 The debug control register

The debug control register is six bits wide. Writes to the debug control register occur

when a watchpoint register is written. Reads of the debug control register occur when a

watchpoint register is read. See Programming and reading watchpoint registers on

page B-43 for more information.

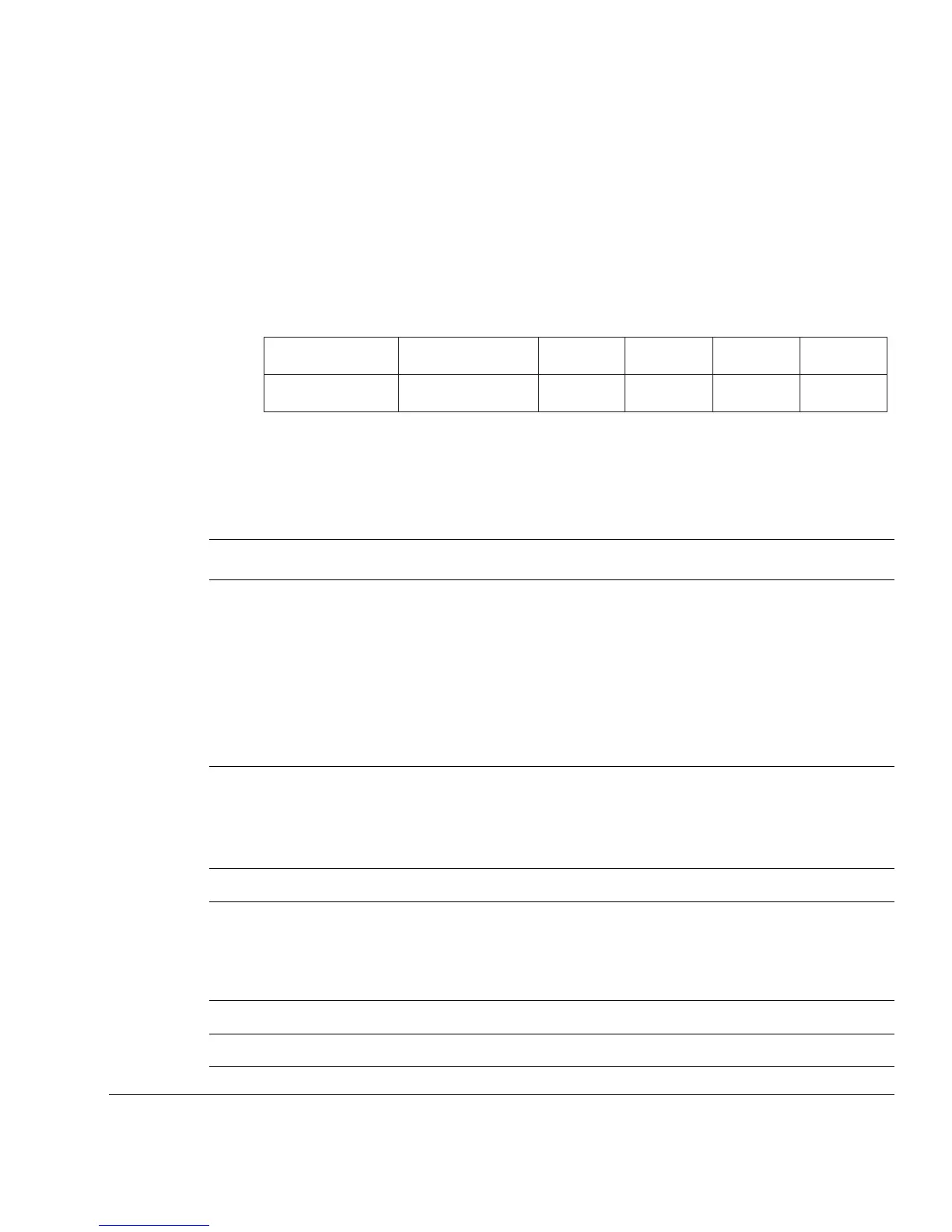

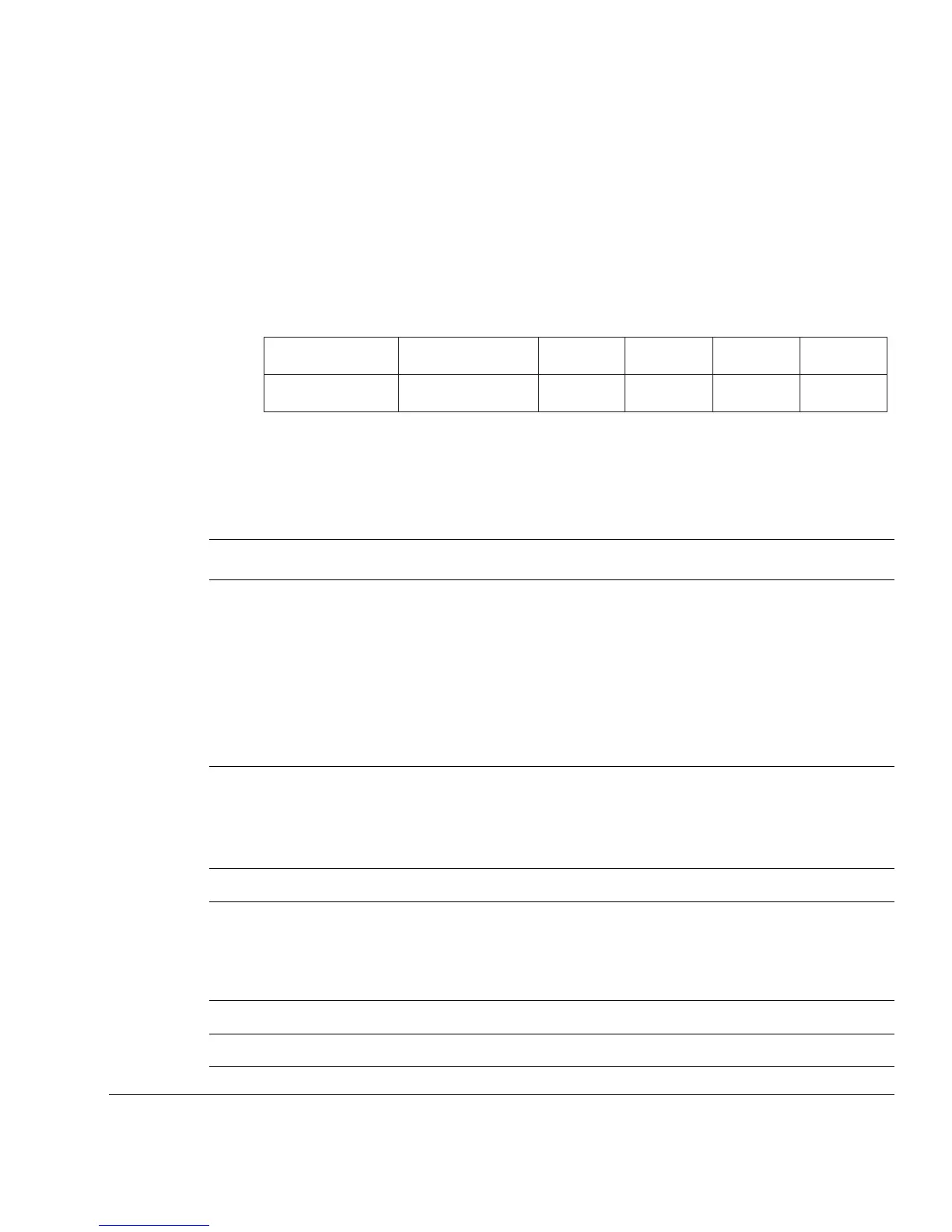

Figure B-9 shows the function of each bit in the debug control register.

Figure B-9 Debug control register format

The debug control register bit assignments are shown in Table B-7.

INTDIS DBGRQ DBGACK

2 1 0

EmbeddedICE-RT

disable

Monitor mode

enable

SBZ/RAZ

5 4 3

Table B-7 Debug control register bit assignments

Bit Function

[5] Used to disable the EmbeddedICE-RT comparator outputs while the watchpoint and breakpoint

registers are being programmed. This bit can be read and written through JTAG.

Set bit [5] when:

• programming breakpoint or watchpoint registers

• changing bit [4] of the debug control register.

You must clear bit [5] after you have made the changes, to re-enable the EmbeddedICE-RT logic.

Bit [5] is writable when the core is synchronized to MCLK, (when it is safe to mask the

comparator outputs), and readable when synchronized to TCK.

[4] Used to determine the behavior of the core when breakpoints or watchpoints are reached:

• If clear, the core enters debug state when a breakpoint or watchpoint is reached.

• If set, the core performs an abort exception when a breakpoint or watchpoint is reached.

This bit can be read and written from JTAG.

[3] This bit must be LOW.

[2] Used to disable interrupts:

• If set, the interrupt enable signal of the core (IFEN) is forced LOW. The IFEN signal is

driven as shown in Table B-8 on page B-52.

• If clear, interrupts are enabled.

[1] Used to force the value on DBGRQ.

[0] Used to force the value on DBGACK.

Loading...

Loading...