Instruction Cycle Timings

ARM DDI 0210C Copyright © 2001, 2004 ARM Limited. All rights reserved. 6-17

6.10 Store multiple registers

The store multiple instruction proceeds very much as load multiple instruction, without

the final cycle. The abort handling is much more straightforward as there is no

wholesale overwriting of registers.

The cycle timings are listed in Table 6-13 where:

• Ra is the first register specified

• R• are the subsequent registers specified.

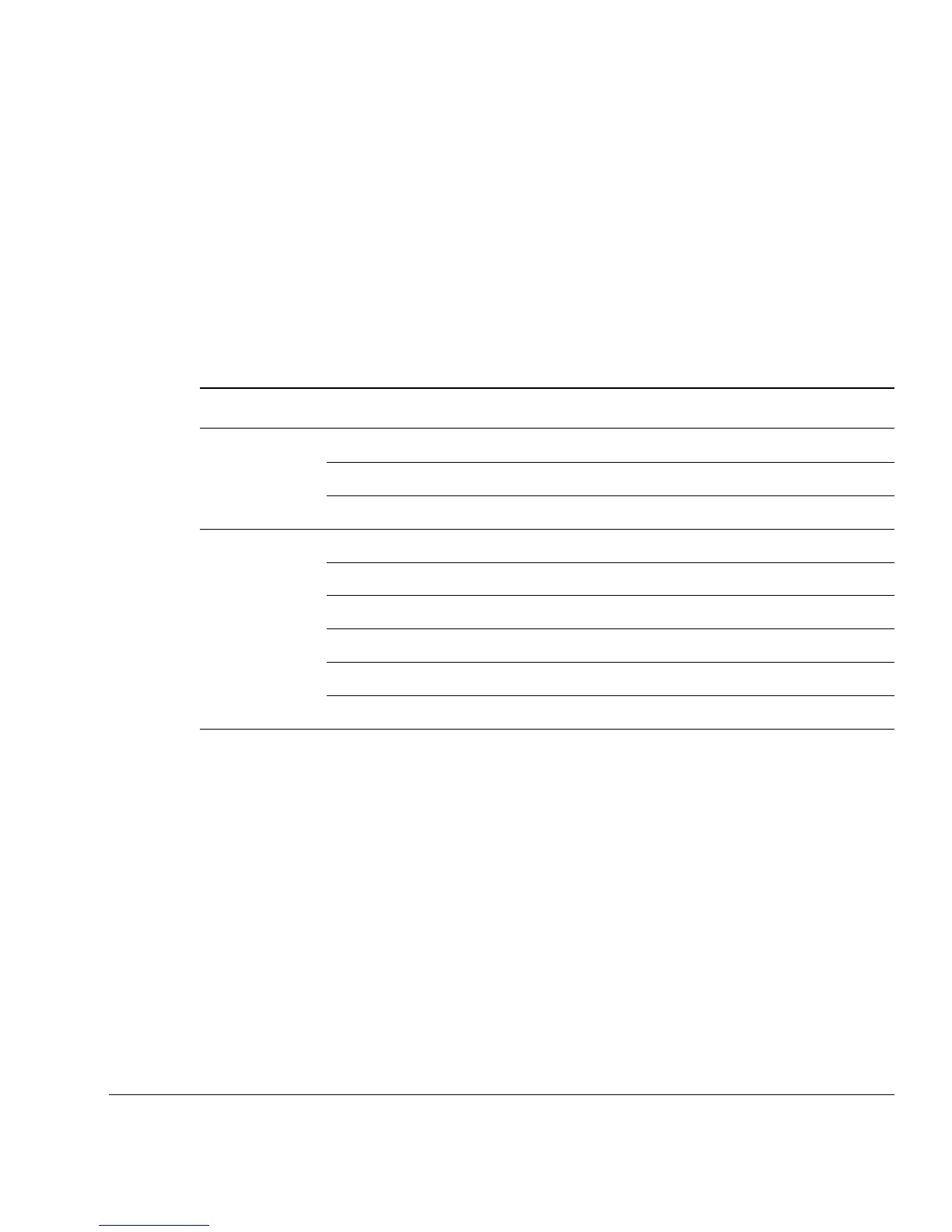

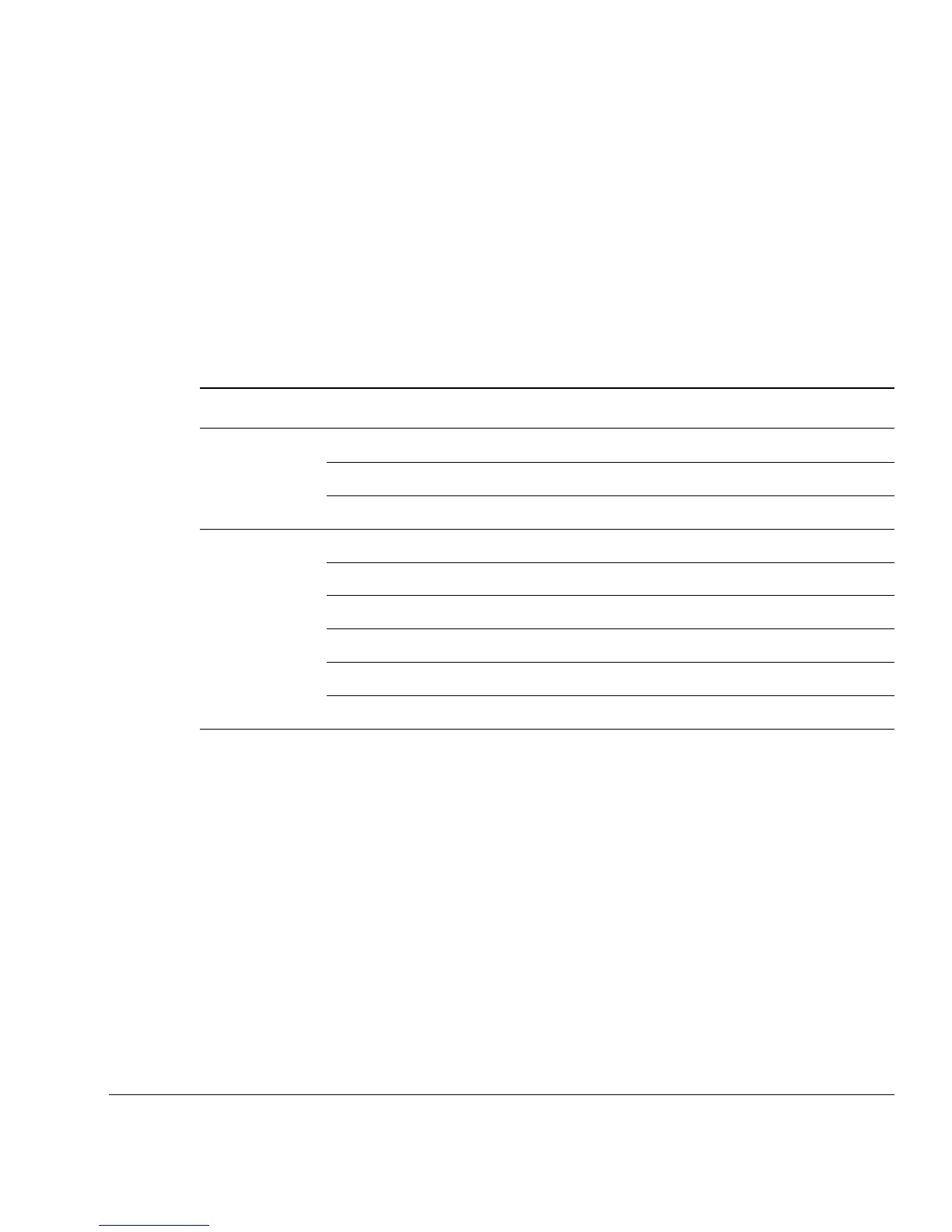

Table 6-13 Store multiple registers instruction cycle operations

Register Cycle Address MAS[1:0] nRW Data nMREQ SEQ nOPC

Single register 1 pc+2L i 0 (pc+2L) 0 0 0

2alu 2 1Ra0 01

pc+3L

n registers (n>1) 1 pc+8 i 0 (pc+2L) 0 0 0

2alu 2 1Ra0 11

•alu+•2 1R•0 11

nalu+•2 1R• 0 11

n+1 alu+• 2 1 R• 0 0 1

pc+12

Loading...

Loading...