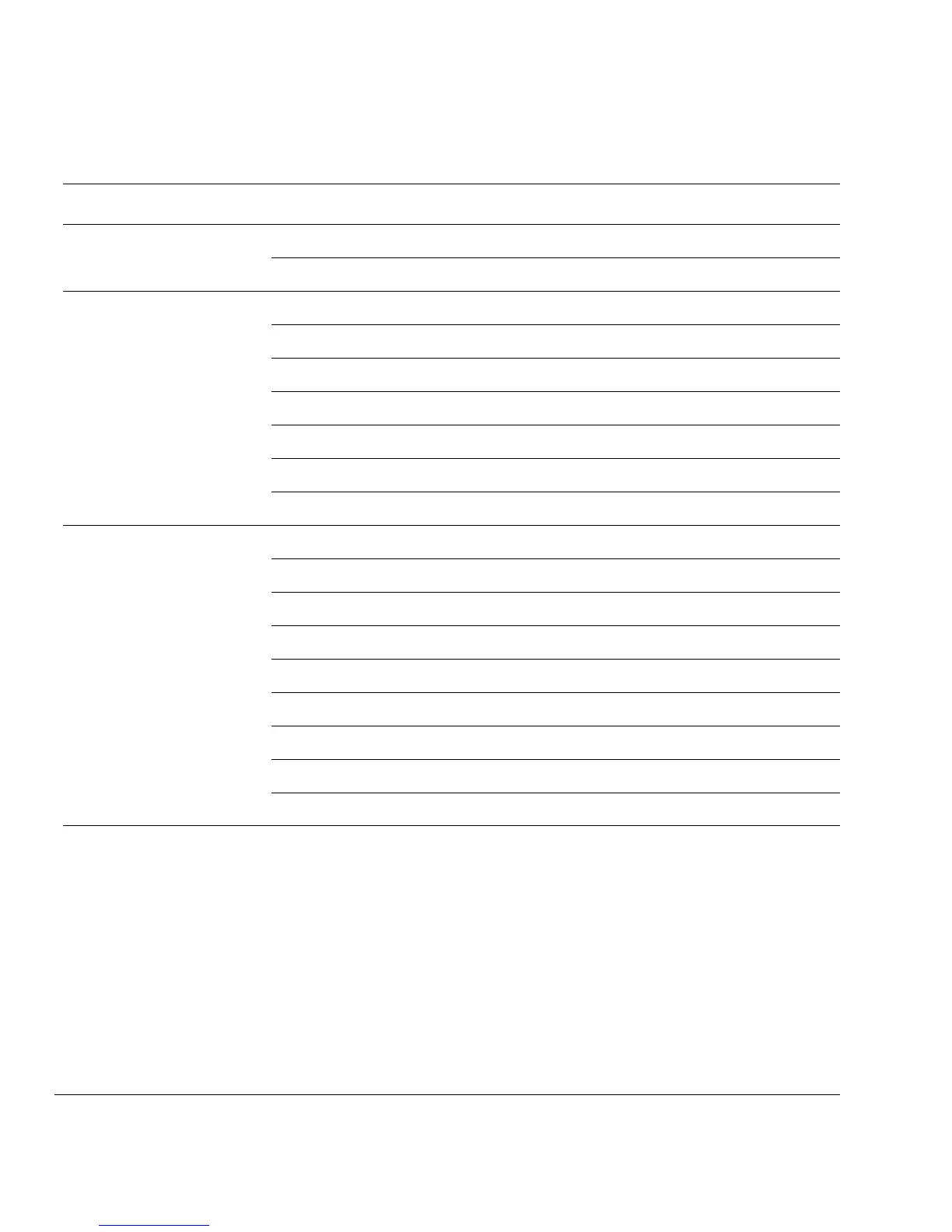

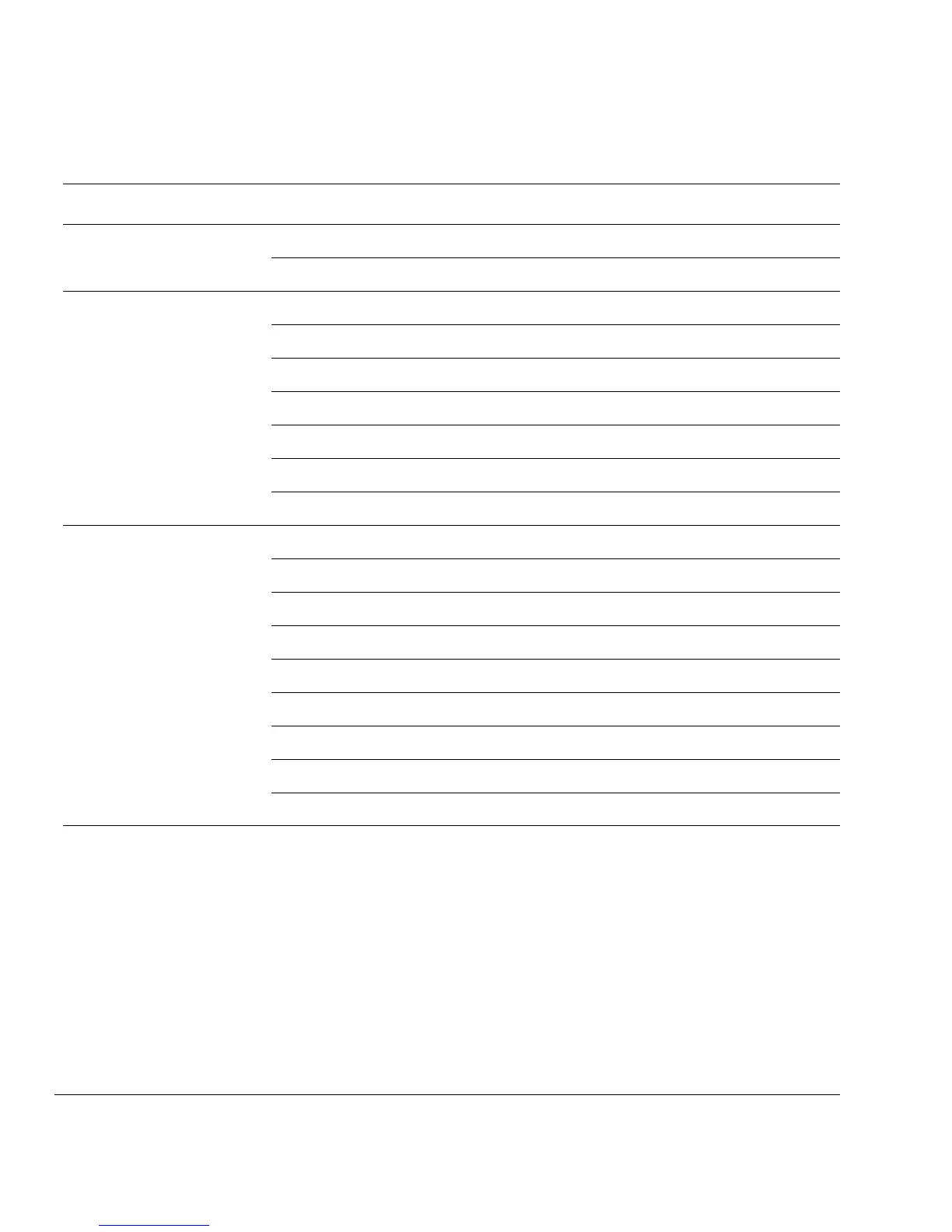

Instruction Cycle Timings

6-16 Copyright © 2001, 2004 ARM Limited. All rights reserved. ARM DDI 0210C

5 pc’+L i 0 (pc’+L) 0 1 0

pc’+2L

n registers (n>1) 1 pc+2L i 0 (pc+2L) 0 0 0

2 alu 2 0 (alu) 0 1 1

• alu+• 2 0 (alu+•) 0 1 1

n alu+• 2 0 (alu+•) 0 1 1

n+1 alu+• 2 0 (alu+•) 1 0 1

n+2 pc+3L i 0 - 0 1 1

pc+3L

n registers (n>1) including pc 1 pc+2L i 0 (pc+2L) 0 0 0

2 alu 2 0 (alu) 0 1 1

• alu+• 2 0 (alu+•) 0 1 1

n alu+• 2 0 (alu+•) 0 1 1

n+1 alu+• 2 0 pc’ 1 0 1

n+2 pc+3L i 0 - 0 0 1

n+3 pc’ i 0 (pc’) 0 1 0

n+4 pc’+L i 0 (pc’+L) 0 1 0

pc’+2L

Table 6-12 Load multiple registers instruction cycle operations (continued)

Destination registers Cycle Address MAS[1:0] nRW Data nMREQ SEQ nOPC

Loading...

Loading...