R&S

®

ZVA / R&S

®

ZVB / R&S

®

ZVT Annexes

Interfaces and Connectors

Operating Manual 1145.1084.12 – 30 1146

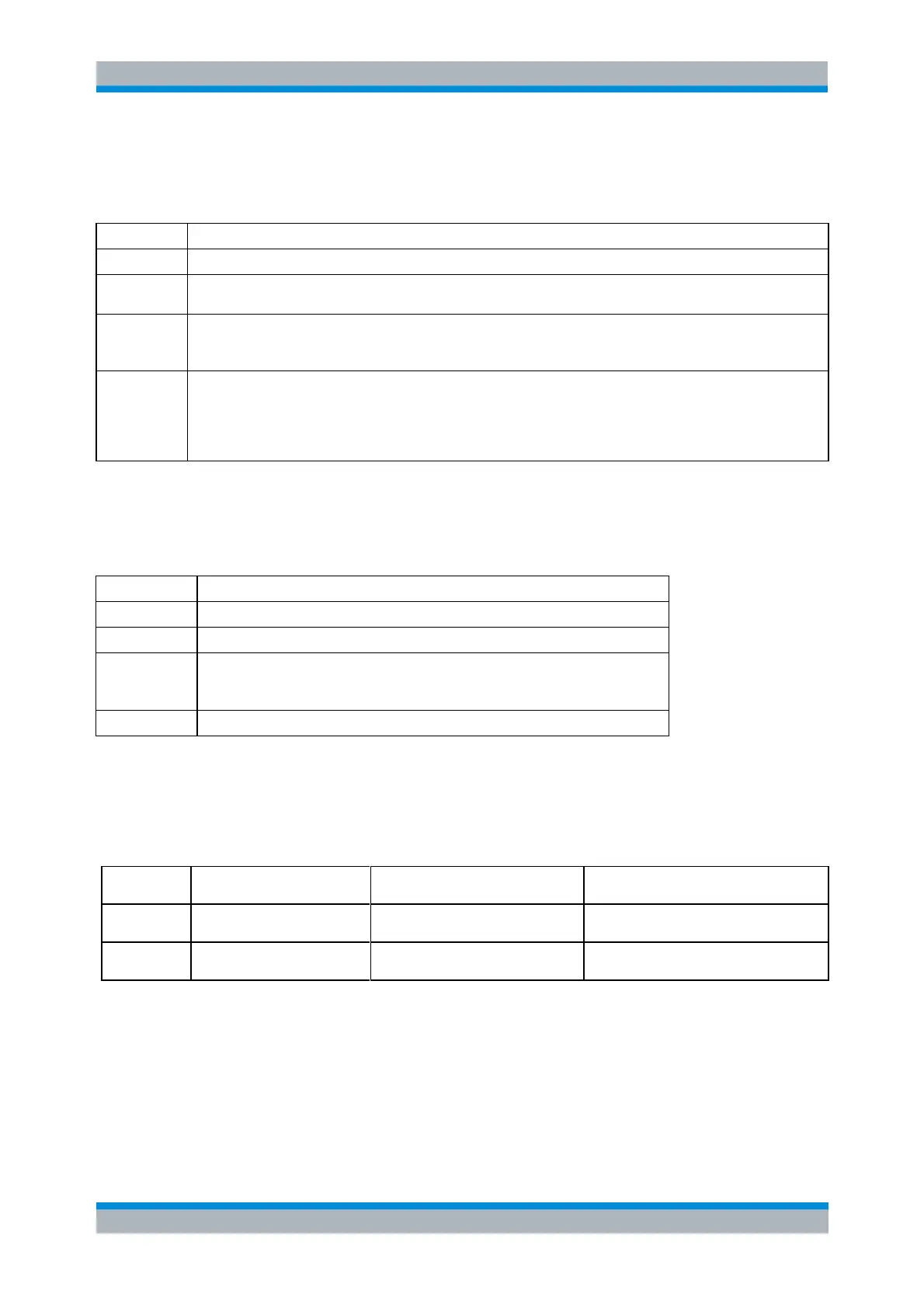

RSDLLWaitSrq

This function waits until the device triggers an SRQ with the handle ud.

Function RSDLLWaitSrq (ByVal ud%, Result%, ibsta%, iberr%, ibcntl&) As Integer

short WINAPI RSDLLWaitSrq( short ud, short far *result, short far *ibsta, short far *iberr, unsigned long far *ibcntl)

short RSDLLWaitSrq( short ud, short *result, short *ibsta, short *iberr, unsigned long *ibcntl)

ud // Device handle

result // Reference to an integer value in which the library returns the status of the SRQ bit (0 - No SRQ has

occurred during the timeout, or 1 - SRQ has occurred during the timeout)

RSDLLWaitSrq( ud, result, ibsta, iberr, ibcntl );

The function waits until one of the following two events occurs:

The measuring instrument triggers an SRQ

No SRQ occurs during the timeout defined with RSDLLibtmo()

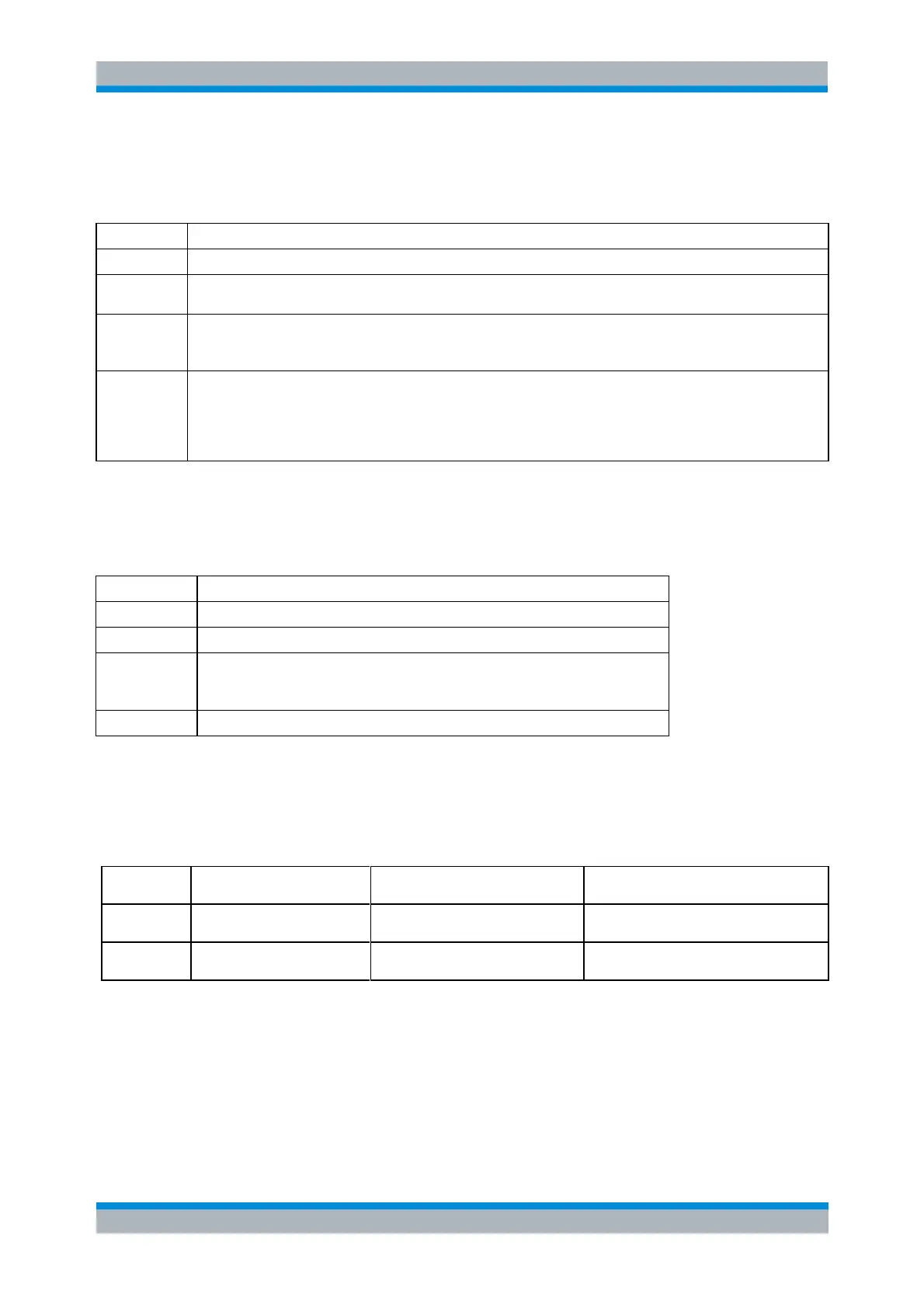

RSDLLSwapBytes

This function changes the display of binary numbers on non-Intel platforms.

Not provided at present since it is required only on non-Intel platforms.

void WINAPI RSDLLSwapBytes( void far *pArray, const long size, const long count)

void RSDLLSwapBytes( void *pArray, const long size, const long count)

pArray // Array in which modifications are made

size // Size of a single element in pArray

count // Number of elements in pArray

RSDLLSwapBytes( Buffer, sizeof(float), ibcntl/sizeof(float))

This function swaps the display of various elements from Big Endian to Little Endian and vice versa. It is

expected that a coherent storage area of elements of the same file type (size byte) is transferred to

pArray. This function has no effect on Intel platforms.

Different types of processor architecture store data in different byte sequences. For example, Intel

processors store data in the reverse order of Motorola processors. Comparison of byte sequences:

Motorola processors, network

standard

Most significant byte at least

significant address

The most significant byte is at the left end

of the word.

Least significant byte at least

significant address

The most significant byte is at the right

end of the word.

IEC/IEEE Bus Interface

The standard instrument is equipped with a GPIB bus (IEC/IEEE bus) interface. The two interface

connectors labeled IEC BUS and IEC SYSTEM BUS are located on the rear panel of the instrument.

The IEC BUS connector is intended for remote control of the analyzer from a controller (slave

GPIB bus connector).

Loading...

Loading...