9

9-24

DMAC

32180 Group User’s Manual (Rev.1.0)

9.2 DMAC Related Registers

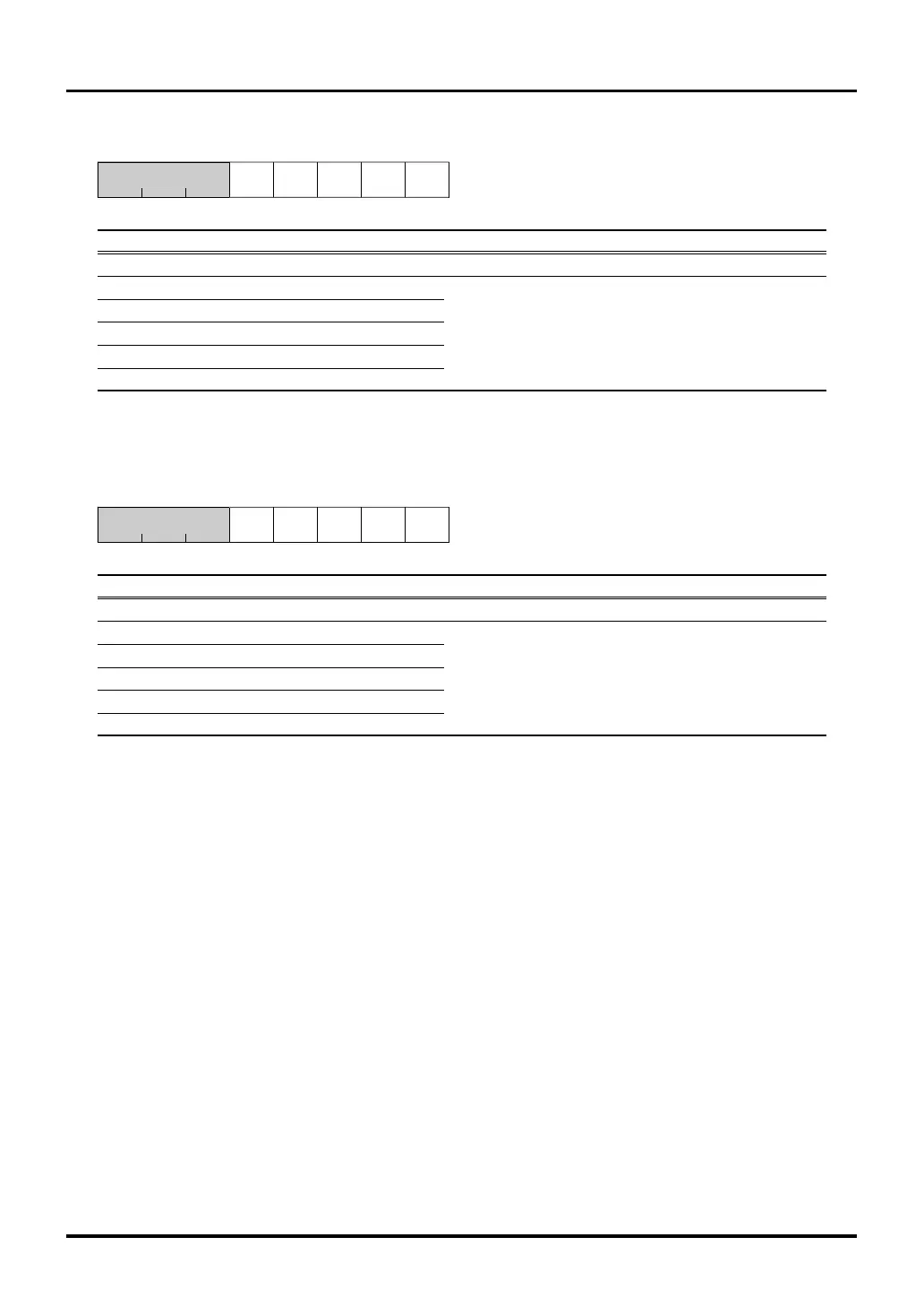

DMA0–4 Interrupt Request Status Register (DM04ITST) <Address: H’0080 0400>

123456b7b0

DMITST4 DMITST3 DMITST1 DMITST0DMITST2

00000

<After reset: H’00>

b Bit Name Function R W

0–2 No function assigned. Fix to "0". 00

3 DMITST4 (DMA4 interrupt request status bit) 0: Interrupt not requested R(Note 1)

4 DMITST3 (DMA3 interrupt request status bit) 1: Interrupt requested

5 DMITST2 (DMA2 interrupt request status bit)

6 DMITST1 (DMA1 interrupt request status bit)

7 DMITST0 (DMA0 interrupt request status bit)

Note 1: Only writing "0" is effective. Writing "1" has no effect; the bit retains the value it had before the write.

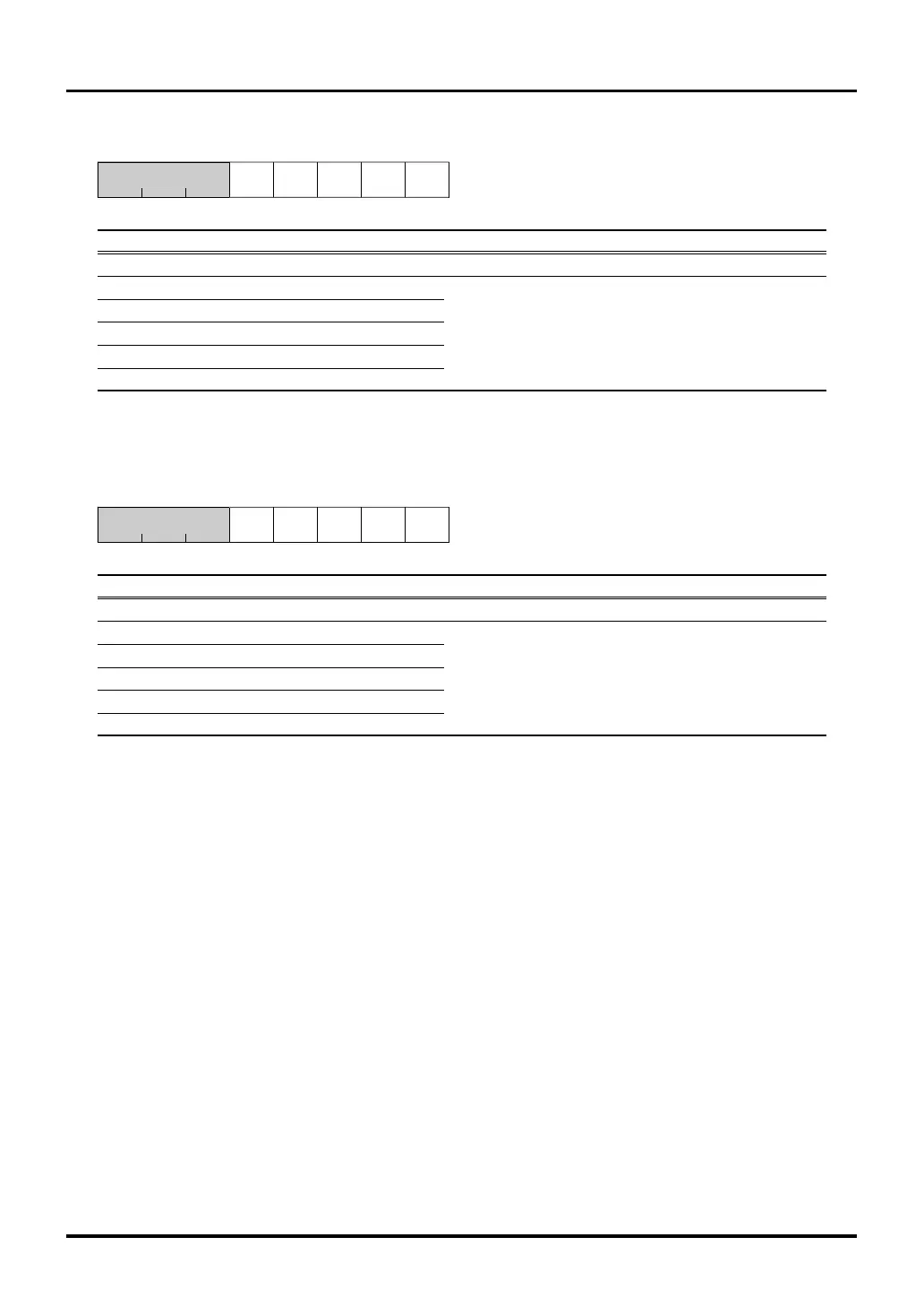

DMA5–9 Interrupt Request Status Register (DM59ITST) <Address: H’0080 0408>

123456b7b0

DMITST9 DMITST8 DMITST6 DMITST5DMITST7

00000

<After reset: H’00>

b Bit Name Function R W

0–2 No function assigned. Fix to "0". 00

3 DMITST9 (DMA9 interrupt request status bit) 0: Interrupt not requested R(Note 1)

4 DMITST8 (DMA8 interrupt request status bit) 1: Interrupt requested

5 DMITST7 (DMA7 interrupt request status bit)

6 DMITST6 (DMA6 interrupt request status bit)

7 DMITST5 (DMA5 interrupt request status bit)

Note 1: Only writing "0" is effective. Writing "1" has no effect; the bit retains the value it had before the write.

The Interrupt Request Status Register helps to know the status of interrupt requests on each channel. If the DMAn

interrupt request status bit (n = 0–9) is set to "1", it means that a DMA interrupt request on the corresponding

channel has been generated.

(1) DMITSTn (DMAn Interrupt Request Status) bit (n = 0–9)

[Setting the DMAn interrupt request status bit]

This bit is set in hardware, and cannot be set in software.

[Clearing the DMAn interrupt request status bit]

This bit is cleared by writing "0" in software.

Note: • The DMAn interrupt request status bit cannot be cleared by writing "0" to the DMA Interrupt

Control Register’s “interrupt request bit” included in the Interrupt Controller.

When writing to the DMA Interrupt Request Status Register, make sure only the bits to be cleared are set to "0"

and all other bits are set to "1". Those bits that have been set to "1" are unaffected by writing in software and

retain the value they had before the write.

Loading...

Loading...