9

DMAC

9-25

32180 Group User’s Manual (Rev.1.0)

9.2 DMAC Related Registers

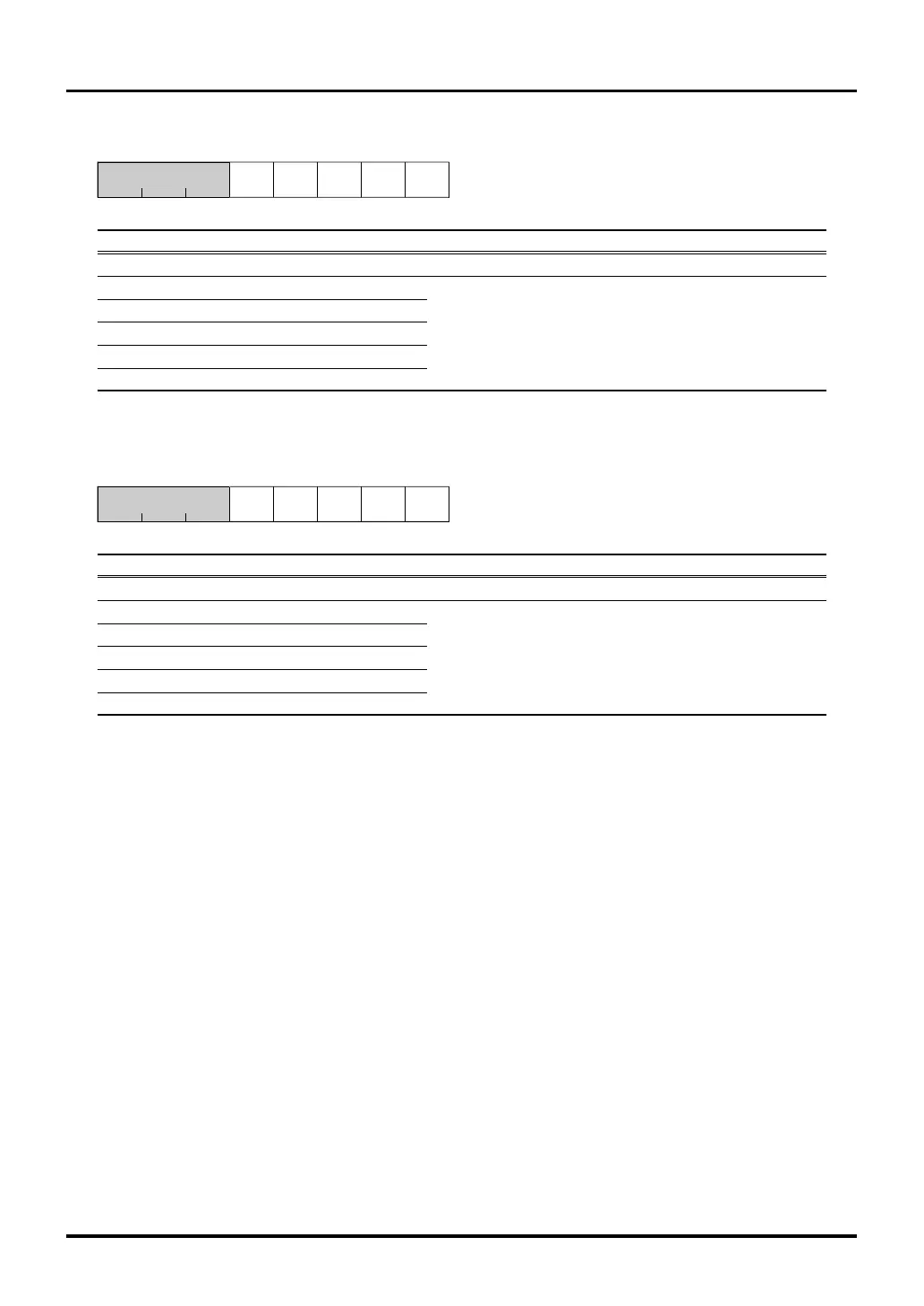

DMA0–4 Interrupt Request Mask Register (DM04ITMK) <Address: H’0080 0401>

9 10 11 12 13 14 b15b8

DMITMK4 DMITMK3 DMITMK1 DMITMK0DMITMK2

00000

<After reset: H’00>

b Bit Name Function R W

8–10 No function assigned. Fix to "0". 00

11 DMITMK4 (DMA4 interrupt request mask bit) 0: Enable interrupt request R W

12 DMITMK3 (DMA3 interrupt request mask bit) 1: Mask (disable) interrupt request

13 DMITMK2 (DMA2 interrupt request mask bit)

14 DMITMK1 (DMA1 interrupt request mask bit)

15 DMITMK0 (DMA0 interrupt request mask bit)

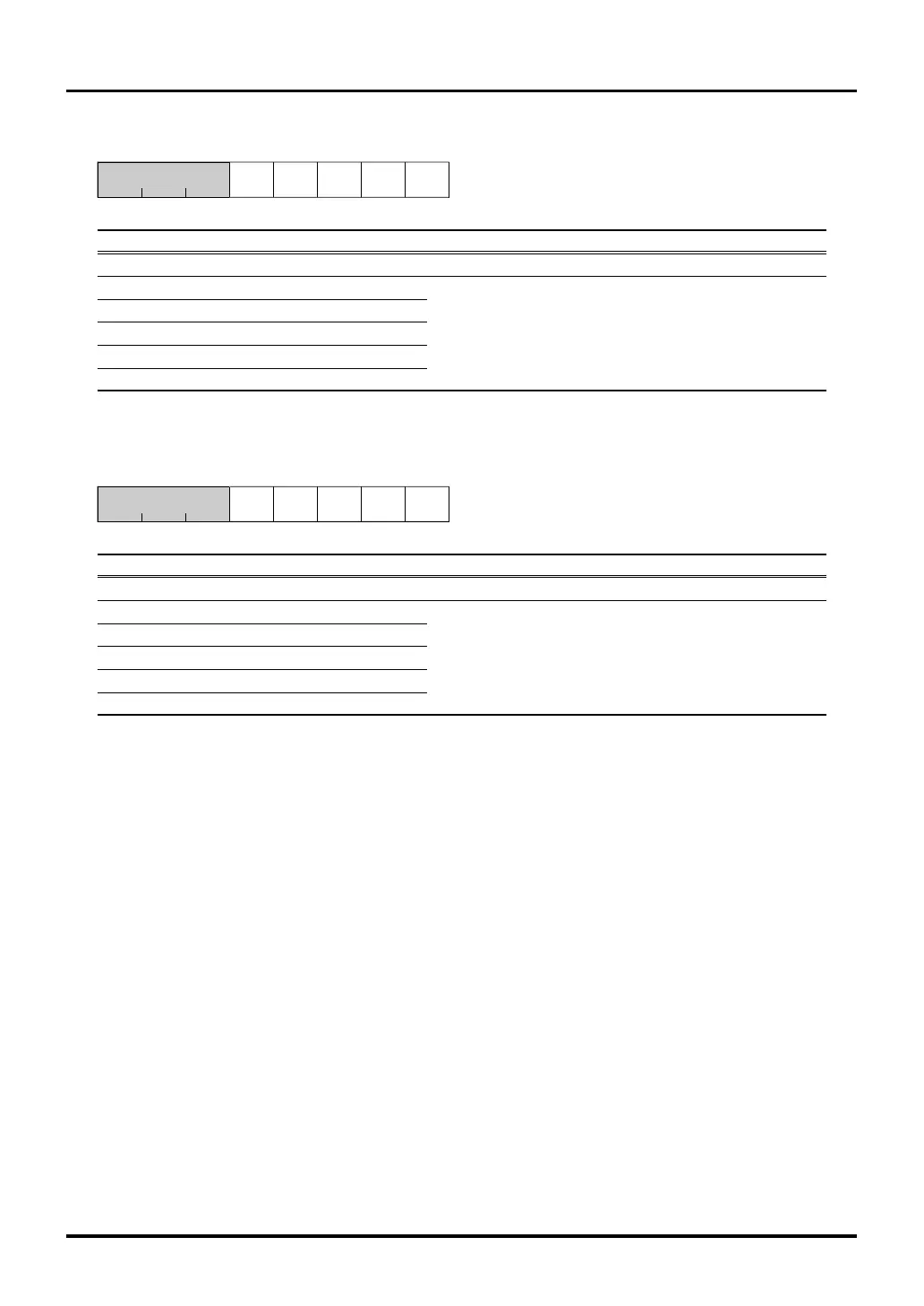

DMA5–9 Interrupt Request Mask Register (DM59ITMK) <Address: H’0080 0409>

9 10 11 12 13 14 b15b8

DMITMK9 DMITMK8 DMITMK6 DMITMK5DMITMK7

00000

<After reset: H’00>

b Bit Name Function R W

8–10 No function assigned. Fix to "0". 00

11 DMITMK9 (DMA9 interrupt request mask bit) 0: Enable interrupt request R W

12 DMITMK8 (DMA8 interrupt request mask bit) 1: Mask (disable) interrupt request

13 DMITMK7 (DMA7 interrupt request mask bit)

14 DMITMK6 (DMA6 interrupt request mask bit)

15 DMITMK5 (DMA5 interrupt request mask bit)

The DMA Interrupt Request Mask Register is used to mask interrupt requests on each DMA channel.

(1) DMITMKn (DMAn Interrupt Request Mask) bit (n = 0–9)

Setting the DMAn interrupt request mask bit to "1" masks the interrupt requests on DMAn channel. However,

if an interrupt request occurs, the DMAn interrupt request status bit is always set to "1" irrespective of the

contents of this mask register.

Loading...

Loading...