9

9-26

DMAC

32180 Group User’s Manual (Rev.1.0)

F/F

F/F

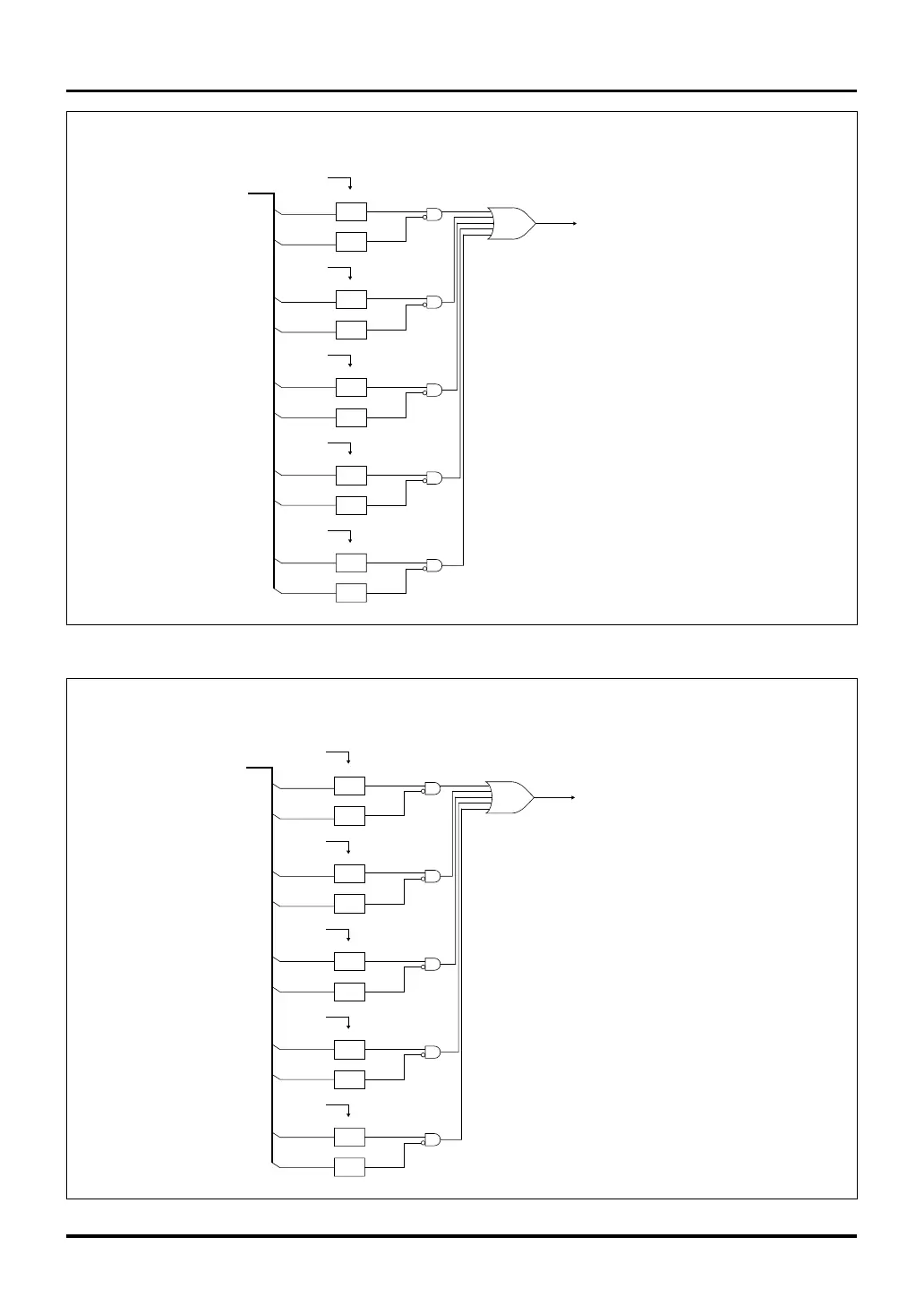

DMITMK5

DMITST5

F/F

F/F

DMITMK6

DMITST6

F/F

F/F

DMITMK7

DMITST7

F/F

F/F

DMITMK8

DMITST8

F/F

F/F

DMITMK9

DMITST9

b15

b7

b14

b6

b13

b5

b12

b4

b11

b3

Data bus

DMA9UDF

DMA8UDF

DMA7UDF

DMA6UDF

DMA5UDF

DMA transfer interrupt request 1

(Level)

5-source inputs

DM59ITST (H'0080 0408)

DM59ITMK (H'0080 0409)

Figure 9.2.5 Block Diagram of DMA Transfer Interrupt Request 1

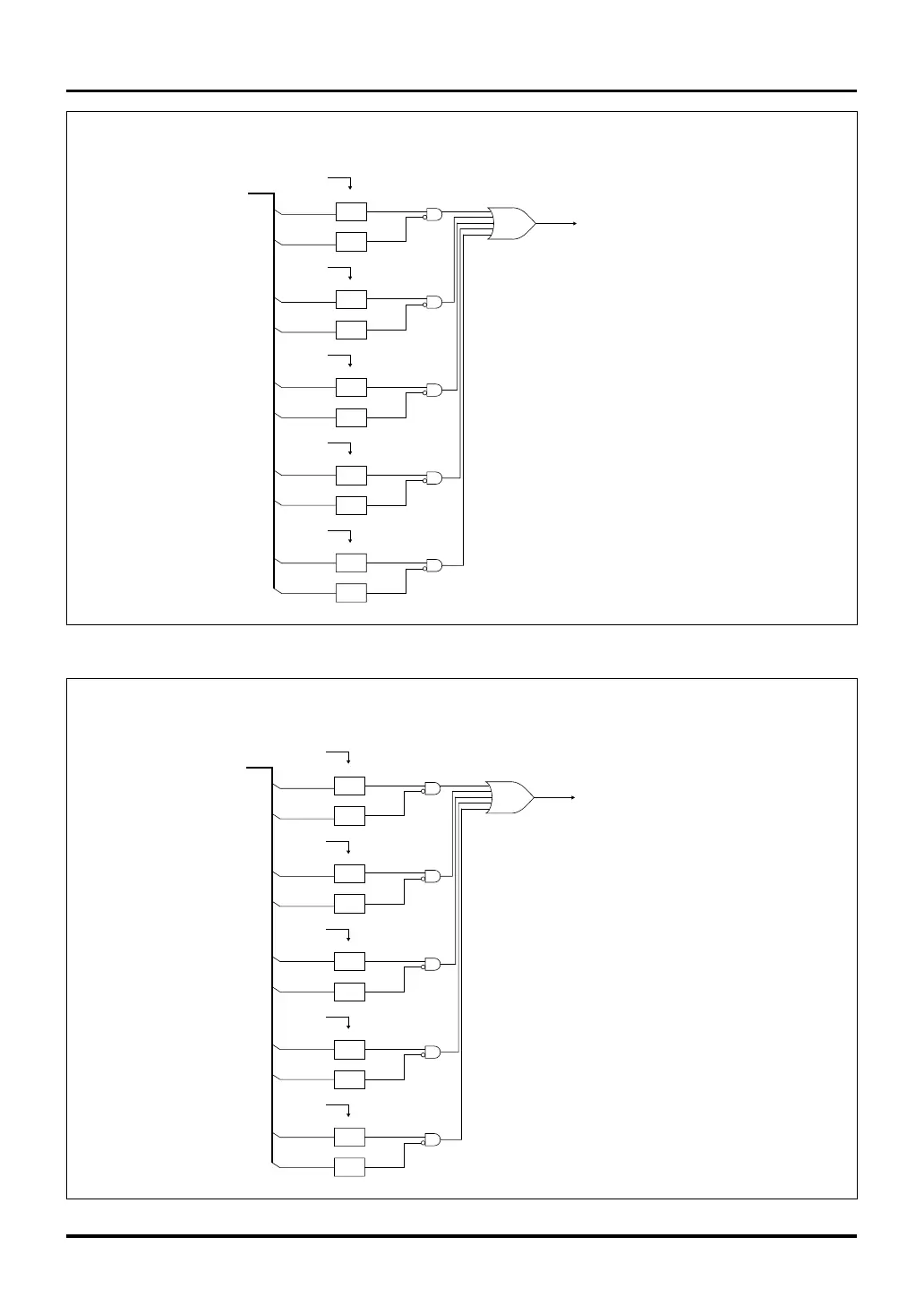

F/F

F/F

DMITMK0

DMITST0

F/F

F/F

DMITMK1

DMITST1

F/F

F/F

DMITMK2

DMITST2

F/F

F/F

DMITMK3

DMITST3

F/F

F/F

DMITMK4

DMITST4

b15

b7

b14

b6

b13

b5

b12

b4

b11

b3

Data bus

DMA4UDF

DMA3UDF

DMA2UDF

DMA1UDF

DMA0UDF

DMA transfer interrupt request 0

(Level)

5-source inputs

DM04ITST (H'0080 0400)

DM04ITMK (H'0080 0401)

Figure 9.2.4 Block Diagram of DMA Transfer Interrupt Request 0

9.2 DMAC Related Registers

Loading...

Loading...