2

2-11

32180 Group User’s Manual (Rev.1.0)

CPU

2.6 Data Formats

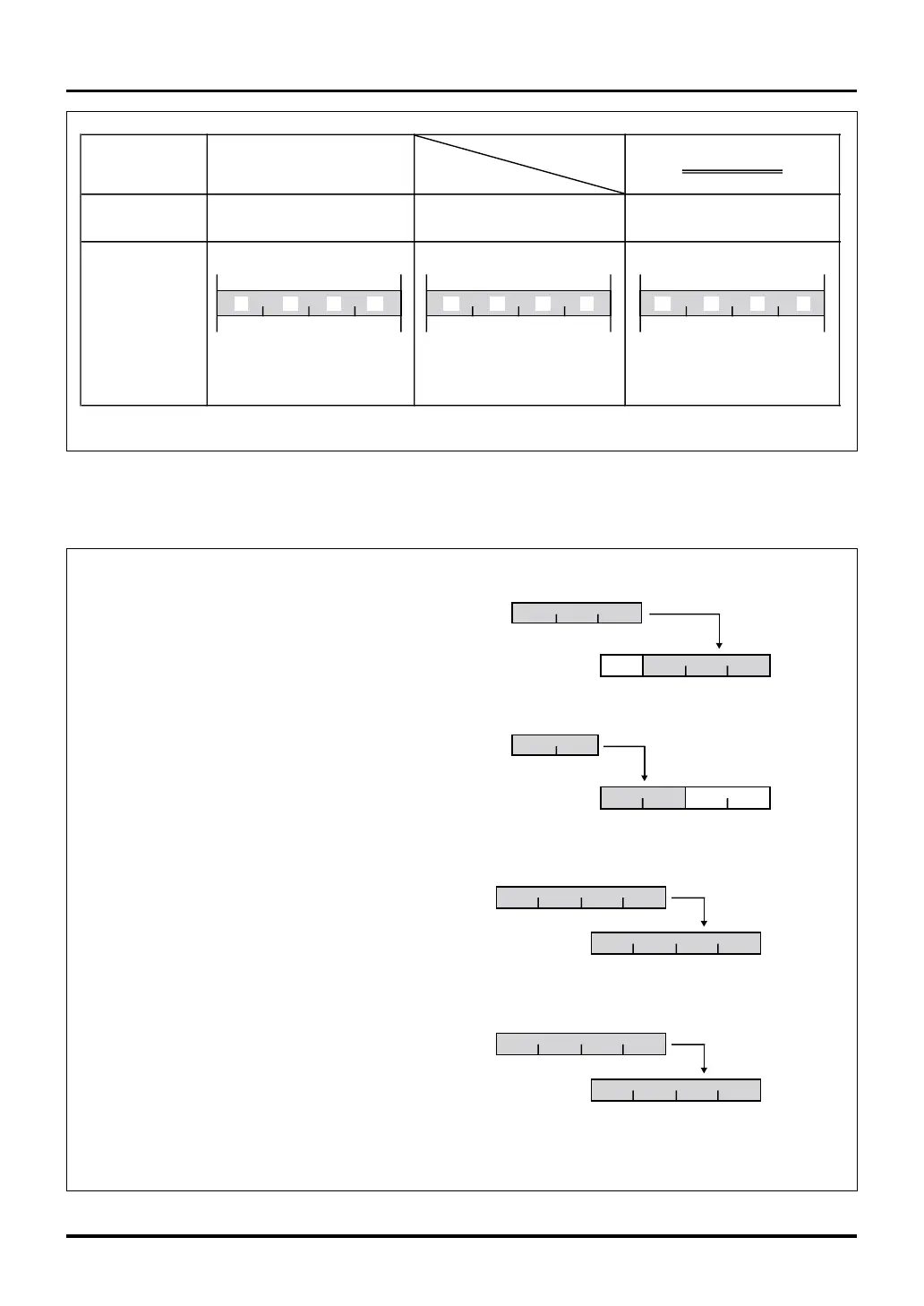

• Constant transfer

LD24 Rdest, #imm24

LDI Rdest, #imm16

LDI Rdest, #imm8

SETH Rdest, #imm16

b23

b0

Rdest

imm24

b31b0

LD24 Rdest, #imm24

b15

b0

Rdest

imm16

b31

b0

SETH Rdest, #imm16

00

8

15

00 00

• Register to register transfer

MV Rdest, Rsrc

• Control register transfer

MVFC Rdest, CRsrc

MVTC Rsrc, CRdest

Rsrc

b31

b0

Rdest

b31b0

Rsrc

b31b0

CRdest

b31b0

MVTC Rsrc, CRdest

MV Rdest, Rsrc

Note: • The condition bit C changes state when data is written to CR0 (PSW) using the MVTC instruction.

Figure 2.6.6 Transfer Instructions

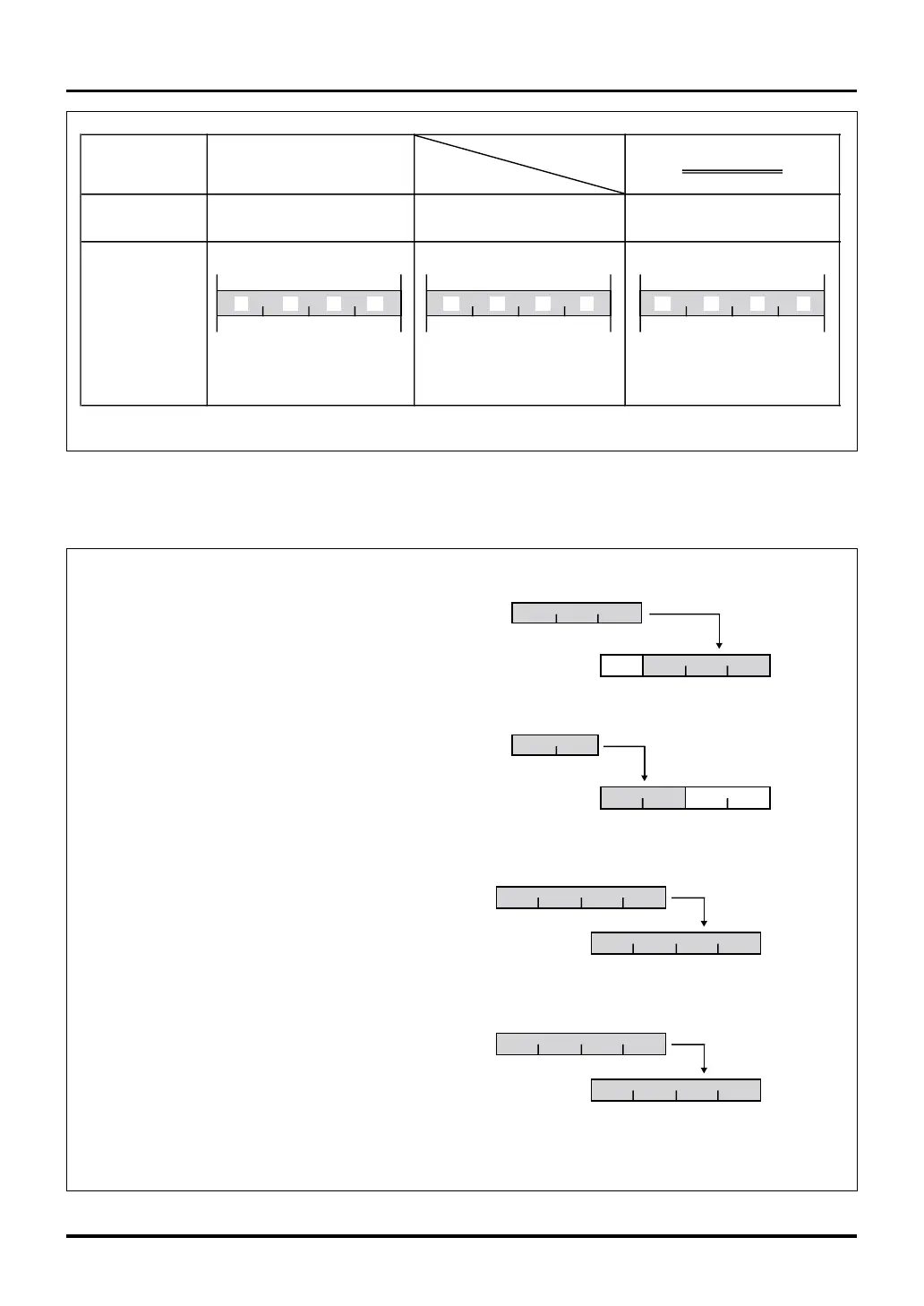

Little/little

LL LH HL HH

Big/big

HH HL LH LL

Little/big

HH HL LH LL

Endian

(bit/byte)

Data arrangement

Mitsubishi

microcomputer

family name

7700 and M16C families

M32R family

31–247–023–1615–80–724–318–15 16–23

Bit number

+0 +1 +2 +3 +0 +1 +2 +3+0 +1 +2 +3

Address

Example:

0x01234567

.byte 67,45,23,01 .byte 01,23,45,67 .byte 01,23,45,67

Note: • The M32R family uses the big endian for both bits and bytes.

7–031–24 15–823–16

Figure 2.6.5 Endian Adopted for the M32R Family

(4) Transfer instructions

Loading...

Loading...