13

13-28

32180 Group User’s Manual (Rev.1.0)

CAN MODULE

13.2 CAN Module Related Registers

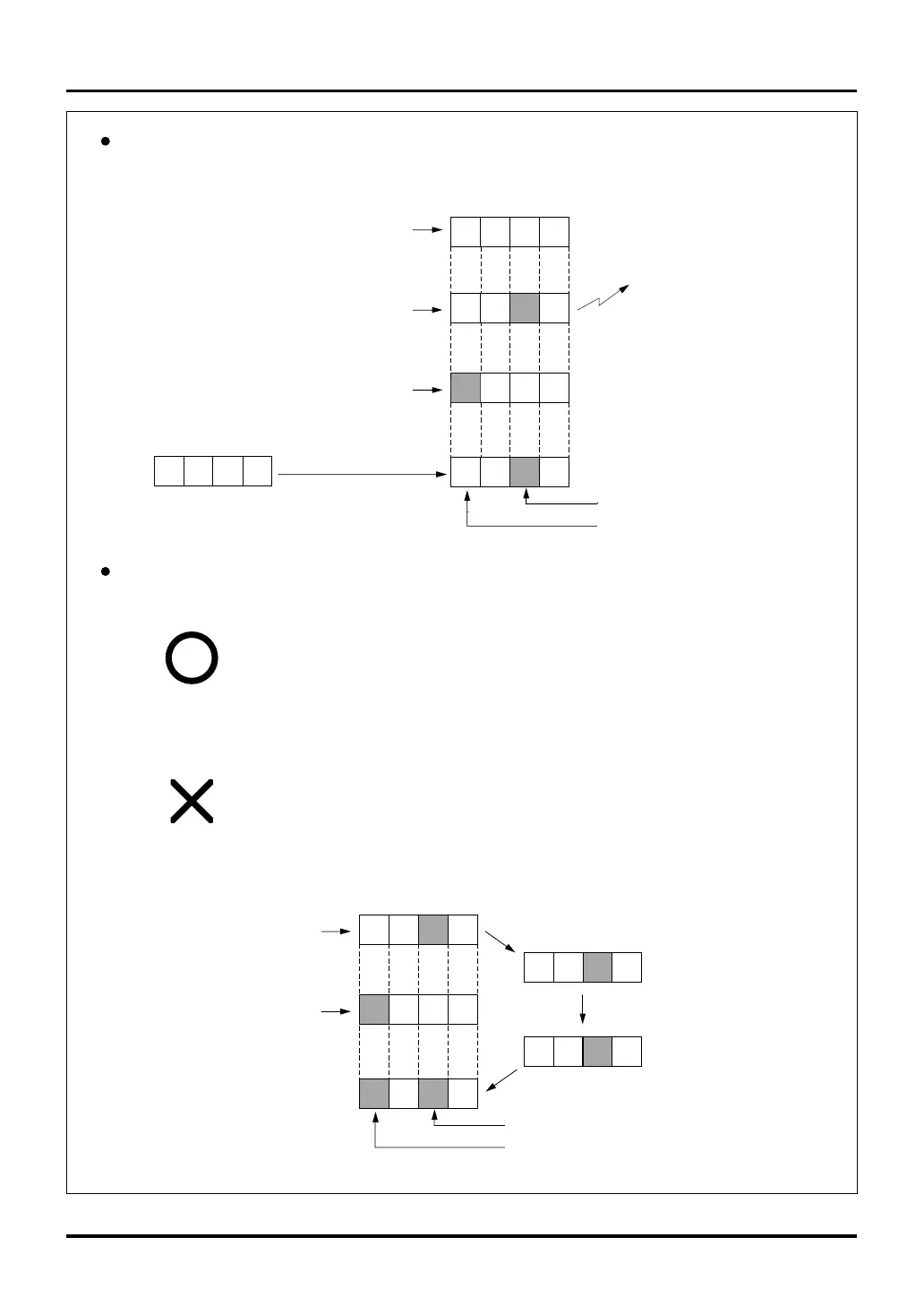

Figure 13.2.1 Interrupt Request Status and Enable Registers

b4 5 b7

Interrupt request status

Initial state

Event occurs on bit 6

Interrupt request

Event occurs on bit 4

Only bit 6 cleared

Bit 4 data retained

b4 5 b7

1 1 0 1

Write to the interrupt request status

Example for clearing interrupt request status

0 0 0 0

0 0 1 0

1 0 1 0

1 0 0 0

Program example

ISTREG = 0xfd; /* Clear ISTAT1 (0x02 bit) only */

• To clear the Interrupt Request Status Register 0 (ISTREG) interrupt request status 1, ISTAT1 (0x02 bit)

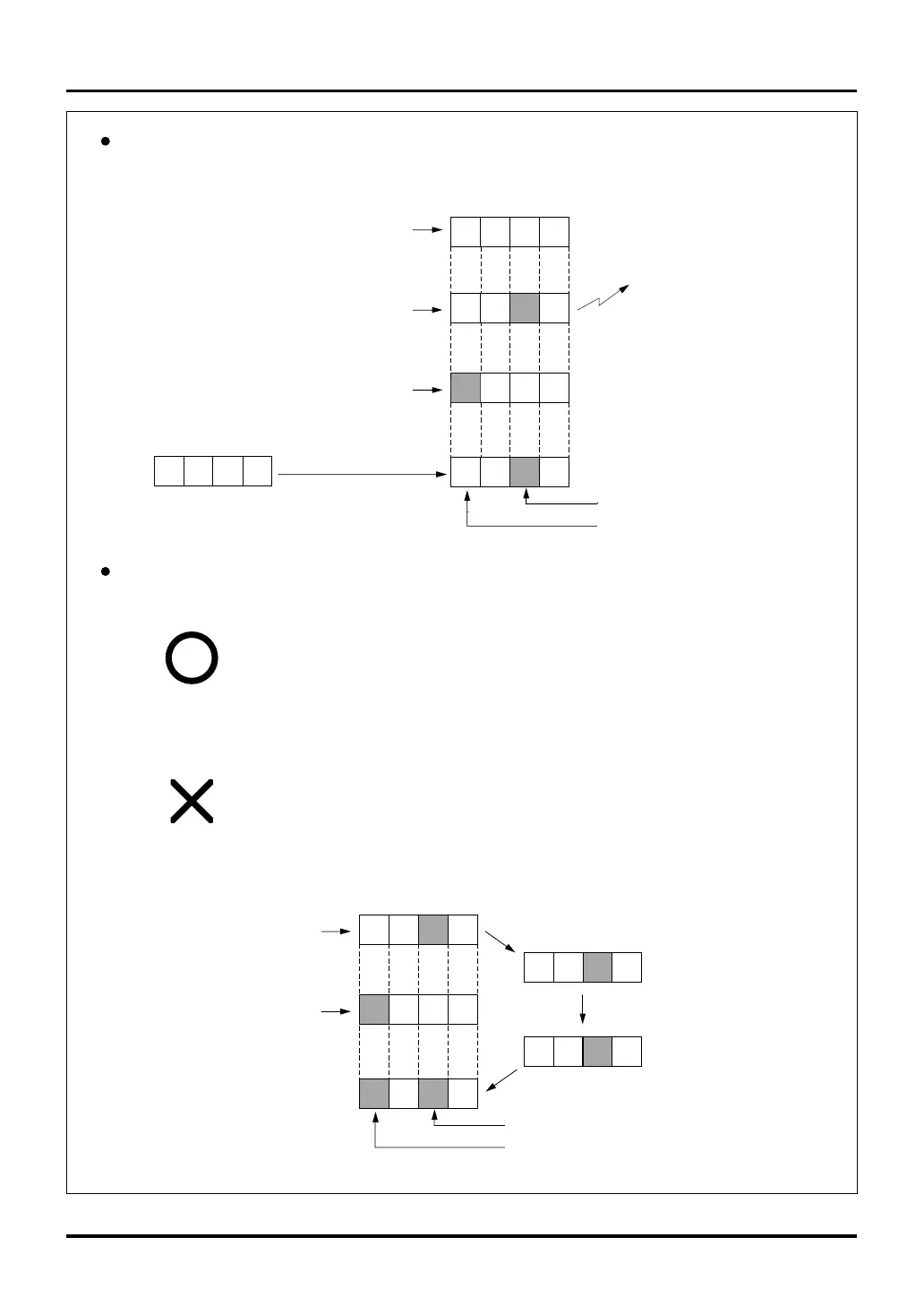

To clear an interrupt request status, always be sure to write 1 to all other interrupt request status bits. At this time,

avoid using a logic operation like the one shown below. Because it requires three step-ISTREG read, logic operation

and write, if another interrupt request occurs between the read and write, status may be inadvertently cleared.

b4 5 6 b7

Interrupt request status

Event occurs on bit 6

Event occurs on bit 4

Only bit 6 cleared

Bit 4 also cleared

0 0 1 0

1 0 1 0

0 0 0 0

Read

0 0 1 0

0 0 0 0

Clear bit 6 (AND'ing with 1101)

Write

6

6

ISTREG &= 0xfd; /* Clear ISTAT1 (0x02 bit) only */

Loading...

Loading...