21

21-30

ELECTRICAL CHARACTERISTICS

32180 Group User's Manual (Rev.1.0)

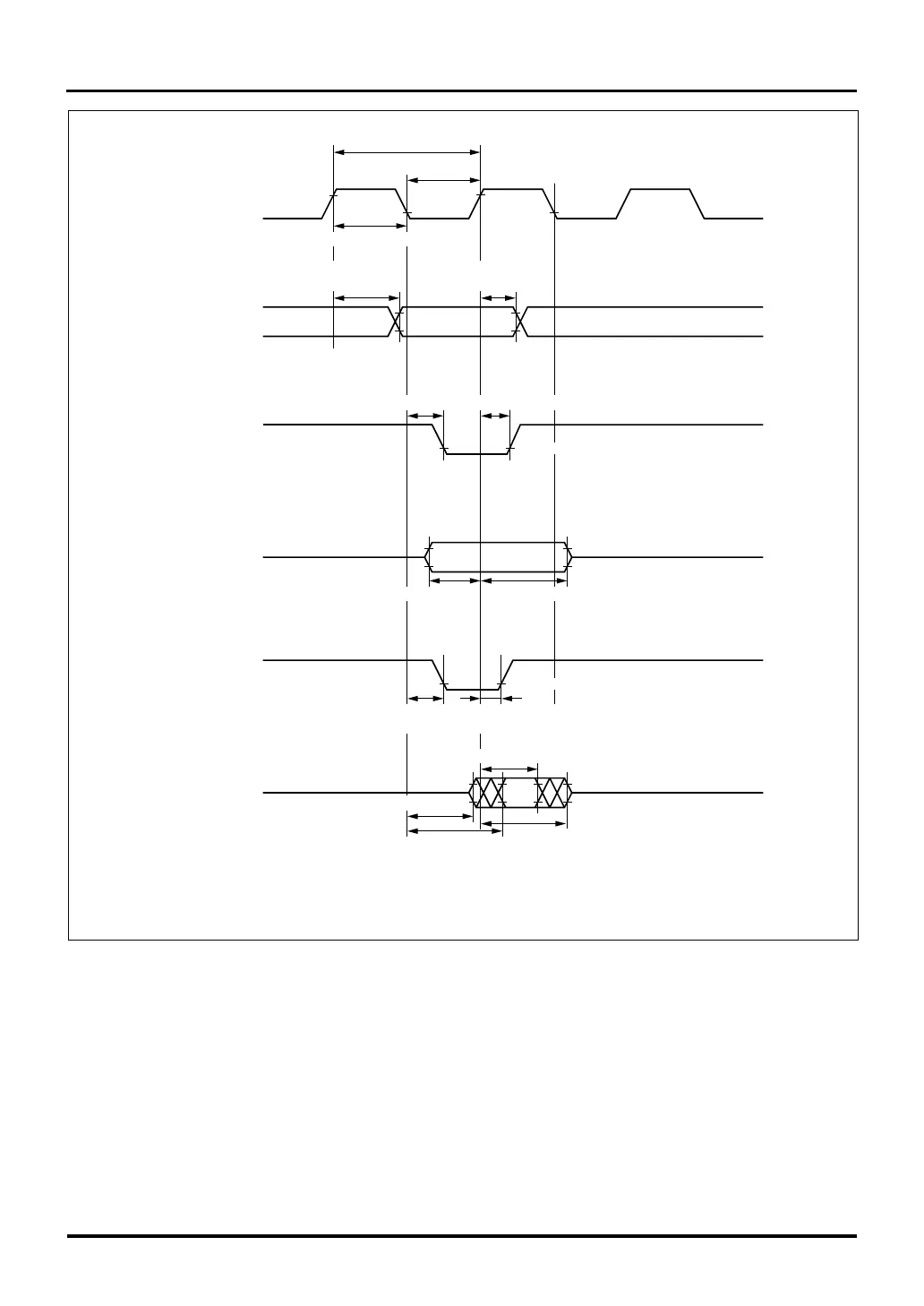

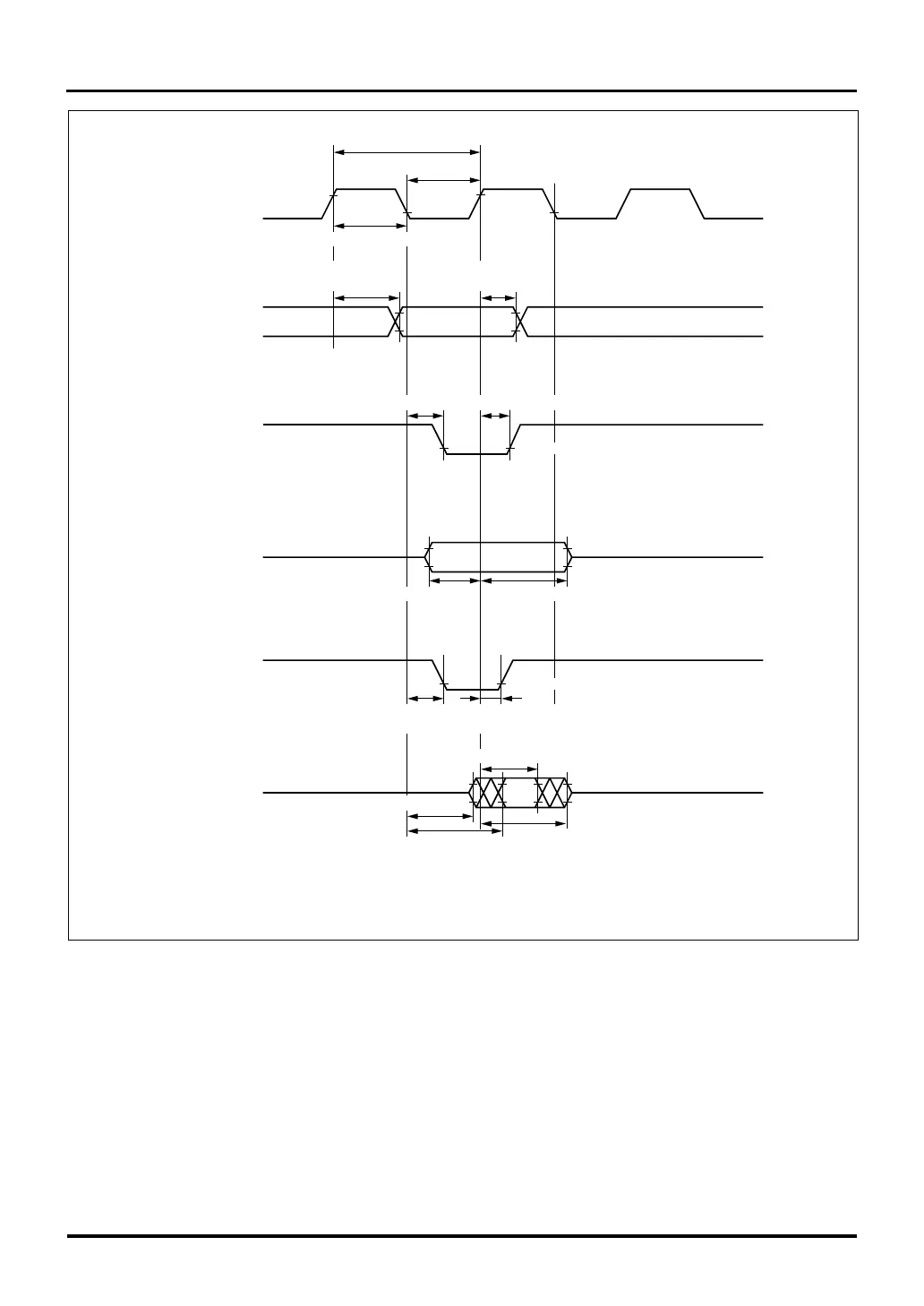

Figure 21.7.7 Read and Write Timing (Relative to BCLK) with Zero Wait State

BCLK

[16]

tc(BCLK)

Data output

(DB0–DB15)

Address

(A11–A30)

CS0#, CS1#,

CS2#, CS3#

BLW#

BHW#

0.43VCC-BUS

0.16VCC-BUS

0.43VCC-BUS

[17] tw(BCLKH)

[18] tw(BCLKL)

[24] tv(BCLKH-RDL)

0.16VCC-BUS

[23] td(BCLKL-RDL)

0.16VCC-BUS

[32] th(BCLKH-D)[31] tsu(D-BCLKH)

[90] tv(BCLKH-BLWL)

tv(BCLKH-BHWL)

[28] tv(BCLKH-D)

[30] tpxz(BCLKH-DZ)

[29] tpzx(BCLKL-DZ)

[27] td(BCLKL-D)

[25] td(BCLKL-BLWL)

td(BCLKL-BHWL)

0.16VCC-BUS

0.43VCC-BUS

0.16VCC-BUS

0.43VCC-BUS

0.16VCC-BUS

RD#

Data input

(DB0–DB15)

[20] td(BCLKH-CS)

[19] td(BCLKH-A)

[22] tv(BCLKH-CS)

[21] tv(BCLKH-A)

Note: • When using the threshold switching function, the data input voltage levels are determined

with respect to the rated minimum and maximum values for VIH and VIL.

21.7 A.C. Characteristics (when VCCE = 5 V)

Loading...

Loading...