9

DMAC

9-29

32180 Group User’s Manual (Rev.1.0)

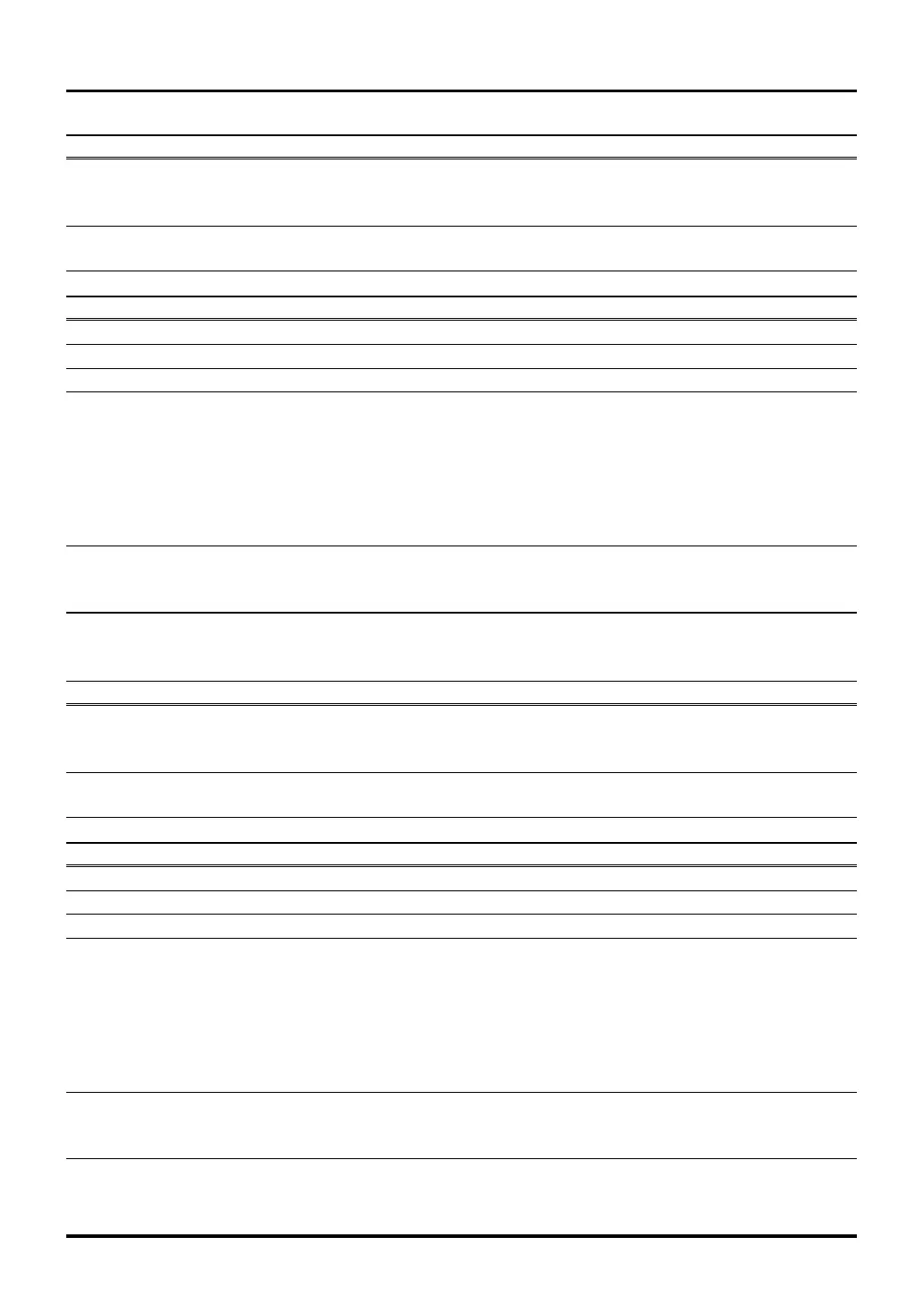

Table 9.3.4 DMA Transfer Request Sources and Generation Timings on DMA3

REQSL3 DMA Transfer Request Source DMA Transfer Request Generation Timing

0 0 Software start When any data is written to the DMA3 Software Request Generation Register

0 1 Serial I/O0 (transmit buffer empty) When serial I/O0 transmit buffer is empty

1 0 Serial I/O1 (reception completed) When serial I/O1 reception is completed

1 1 Extended DMA3 transfer request The source selected by the DMA3 Channel Control Register 1 (DM3CNT1)

source selected REQESEL3 bits (see below)

REQESEL3 DMA Transfer Request Source DMA Transfer Request Generation Timing

0000 MJT (TIN0 input signal) When MJT TIN0 input signal is generated

0001 One DMA2 transfer completed When one DMA2 transfer is completed (cascade mode)

0010 A-D1 conversion completed When A-D1 conversion is completed

0011 MJT (input event bus 1) When MJT input event bus 1 signal is generated

0100 MJT (input event bus 3) When MJT input event bus 3 signal is generated

0101 MJT (output event bus 2) When MJT output event bus 2 signal is generated

0110 MJT (output event bus 3) When MJT output event bus 3 signal is generated

0111 A-D0 conversion completed When A-D0 conversion is completed

1000 MJT (TIN0 input signal) When MJT TIN0 input signal is generated

1001 MJT (TIO8_udf) When MJT TIO8 underflow occurs

1010

| Settings inhibited –

1111

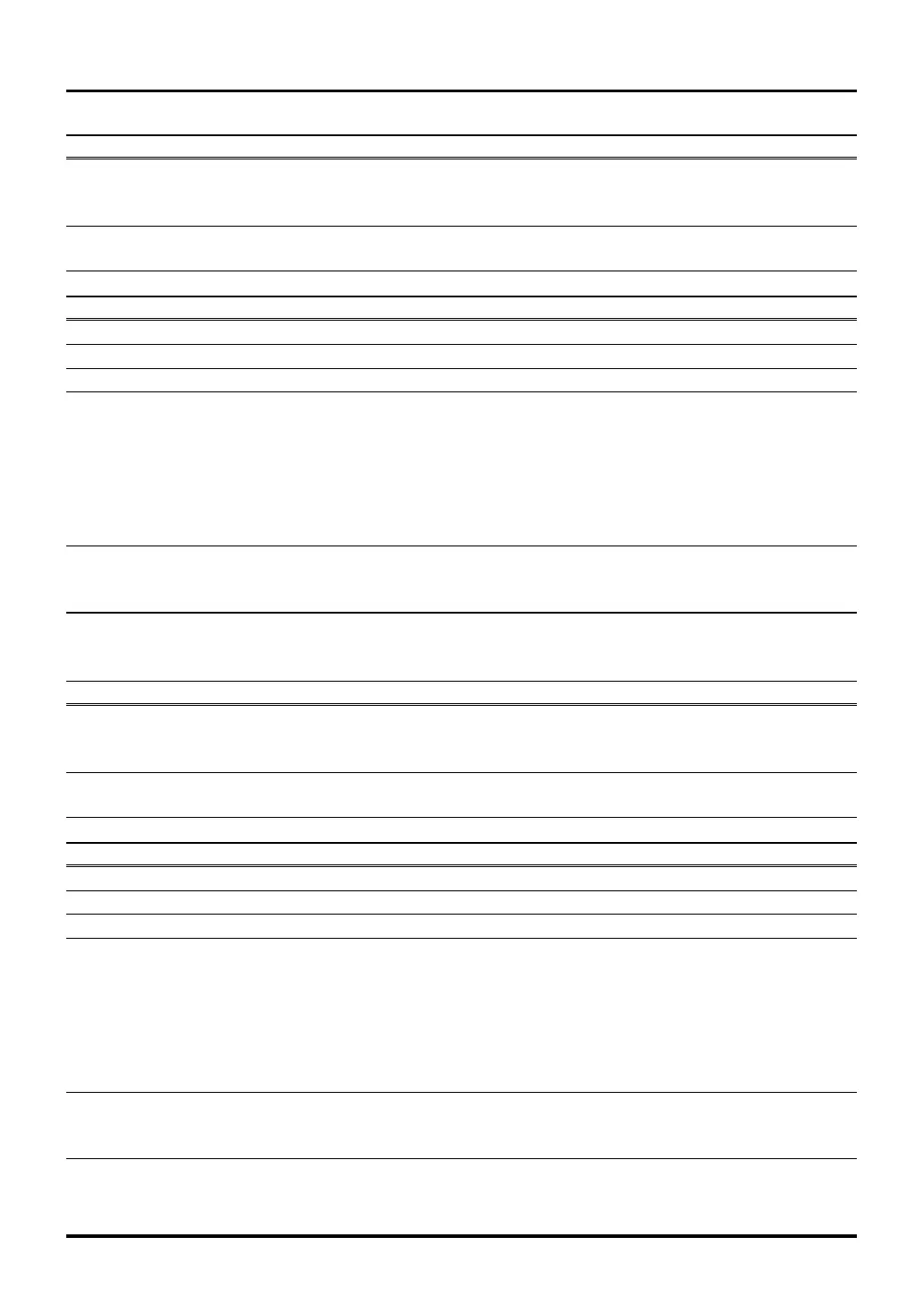

Table 9.3.5 DMA Transfer Request Sources and Generation Timings on DMA4

REQSL4 DMA Transfer Request Source DMA Transfer Request Generation Timing

0 0 Software start When any data is written to the DMA4 Software Request Generation Register

0 1 One DMA3 transfer completed When one DMA3 transfer is completed (cascade mode)

1 0 Serial I/O0 (reception completed) When serial I/O0 reception is completed

1 1 Extended DMA4 transfer request The source selected by the DMA4 Channel Control Register 1 (DM4CNT1)

source selected REQESEL4 bits (see below)

REQESEL4 DMA Transfer Request Source DMA Transfer Request Generation Timing

0000 MJT (TIN19 input signal) When MJT TIN19 input signal is generated

0001 Serial I/O0 (transmit buffer empty) When serial I/O0 transmit buffer is empty

0010 MJT (TOU1_7irq) MJT TOU1_7 interrupt source

0011 MJT (input event bus 1) When MJT input event bus 1 signal is generated

0100 MJT (input event bus 3) When MJT input event bus 3 signal is generated

0101 MJT (output event bus 2) When MJT output event bus 2 signal is generated

0110 MJT (output event bus 3) When MJT output event bus 3 signal is generated

0111 A-D0 conversion completed When A-D0 conversion is completed

1000 MJT (TIN0 input signal) When MJT TIN0 input signal is generated

1001 MJT (TIO8_udf) When MJT TIO8 underflow occurs

1010

| Settings inhibited –

1111

9.3 Functional Description of the DMAC

Loading...

Loading...