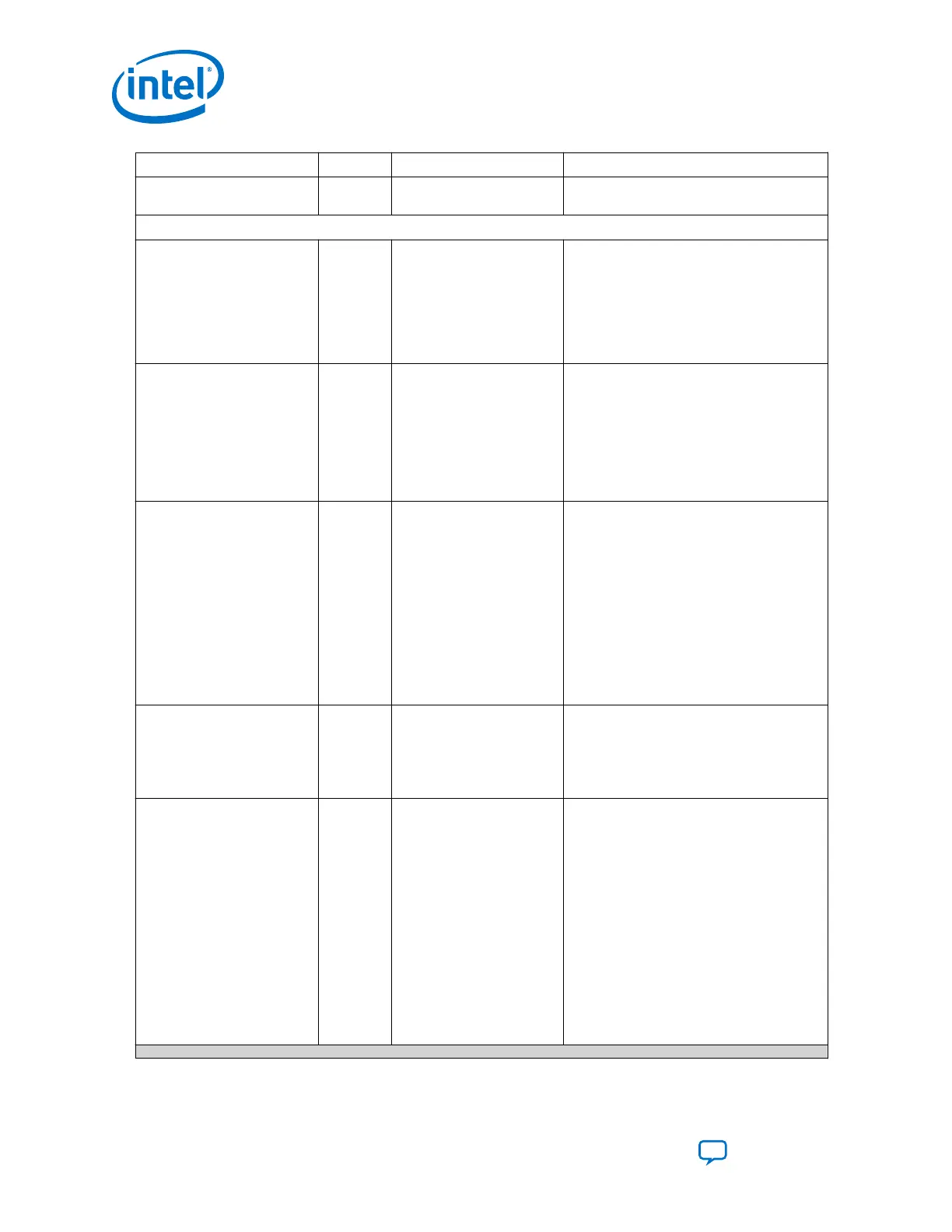

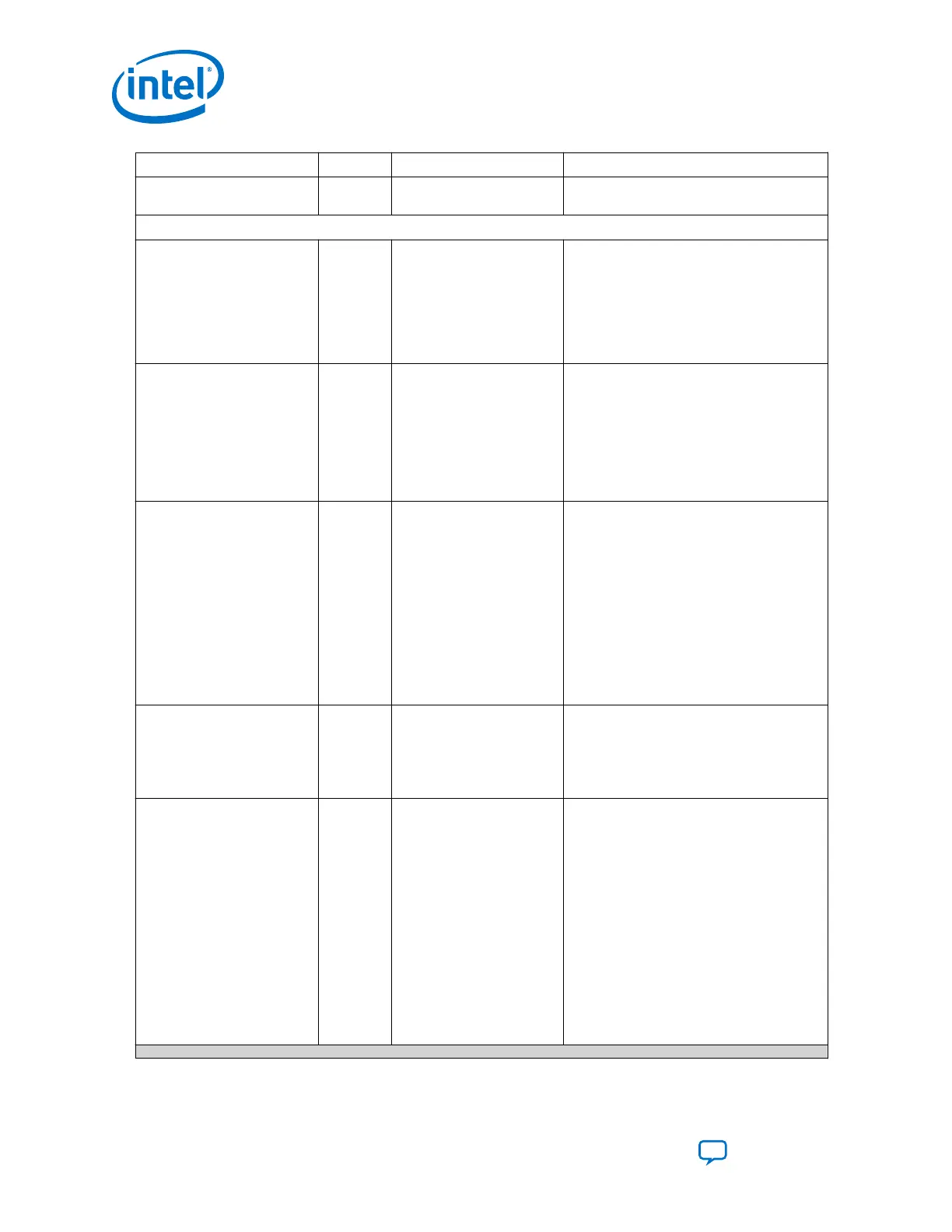

Port Direction Clock Domain Description

pipe_hclk_out[0]

Out N/A

The 500 MHz clock output provided to the

PHY - MAC interface.

PIPE Input from PHY - MAC Layer

tx_parallel_data[15:0]

or [7:0]

In

tx_coreclkin

The TX parallel data driven from the MAC.

For Gen1 this can be 8 or 16 bits. For Gen2

this is 16 bits.

Note: unused_tx_parallel_data should

be tied to '0'.

Active High. Refer to table Bit Mappings when

the Simplified Interface is Disabled for

additional details.

tx_datak[1:0] or [0]

In

tx_coreclkin

The data and control indicator for the

transmitted data.

For Gen1 or Gen2, when 0, indicates that

tx_parallel_data is data, when 1,

indicates that tx_parallel_data is

control.

Active High. Refer to table Bit Mappings when

the Simplified Interface is Disabled for

additional details.

pipe_tx_elecidle[(4N-1)

:0]

In Asynchronous

Forces the transmit output to electrical idle.

Refer to the Intel PHY Interface for PCI

Express (PIPE) for timing diagrams.

Gen1 - Width of signal is 1 bit/lane.

Gen2 - Width of signal is 2 bits/lane. For

example, if the MAC connected to PIPE

Gen2x4 has 1bit/lane, then you can use the

following mapping to connect to PIPE:

{pipe_tx_elecidle[7:0] =

{{2{tx_elecidle_ch3}},

{2{tx_elecidle_ch2}},{2{tx_elecidle_ch1}},

{2{tx_elecidle_ch0}}} where tx_elecidle_*

is the output signal from MAC.

Active High

pipe_tx_detectrx_loopba

ck [(N-1):0]

In

tx_coreclkin

Instructs the PHY to start a receive detection

operation. After power-up, asserting this

signal starts a loopback operation. Refer to

section 6.4 of the Intel PHY Interface for PCI

Express (PIPE) for a timing diagram.

Active High

pipe_tx_compliance[(4N-

1):0]

In

tx_coreclkin

Asserted for one cycle to set the running

disparity to negative. Used when transmitting

the compliance pattern. Refer to section 6.11

of the Intel PHY Interface for PCI Express

(PIPE) Architecture for more information.

Gen1 - Width of signal is 1 bit/lane.

Gen2 - Width of signal is 2 bits/lane.

For example, if the MAC connected to PIPE

Gen2x4 has 1bit/lane, then you can use the

following mapping to connect to PIPE:

{pipe_tx_compliance[7:0] =

{{2{tx_compliance_ch3}},

{2{tx_compliance _ch2}},

{2{tx_compliance_ch1}}, {2{tx_compliance

_ch0}}}. Where tx_compliance_* is the

output signal from MAC.

Active High

continued...

2. Implementing Protocols in Intel Cyclone 10 GX Transceivers

UG-20070 | 2018.09.24

Intel

®

Cyclone

®

10 GX Transceiver PHY User Guide

Send Feedback

140

Loading...

Loading...