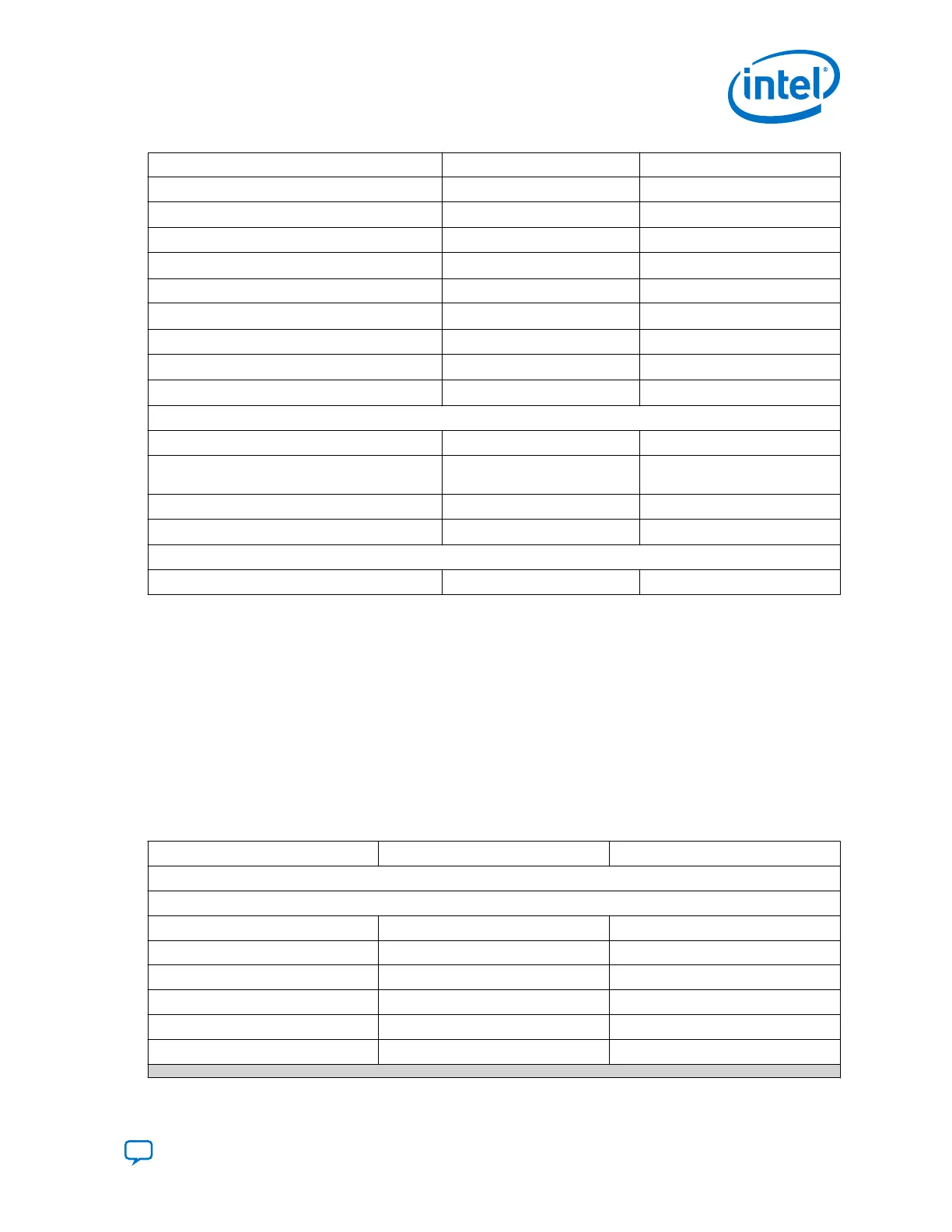

Parameter Gen1 PIPE Gen2 PIPE

Enable TX polarity inversion Off Off

Enable tx_polinv port

Off Off

Enable RX bit reversal Off Off

Enable rx_std_bitrev_ena port

Off Off

Enable RX byte reversal Off Off

Enable rx_std_byterev_ena port

Off Off

Enable RX polarity inversion Off Off

Enable rx_polinv port

Off Off

Enable rx_std_signaldetect port

Optional Optional

PCIe Ports

Enable PCIe dynamic datarate switch ports Off Enabled

Enable PCIe pipe_hclk_in and pipe_hclk_out

ports

Enabled Enabled

Enable PCIe electrical idle control and status ports Enabled Enabled

Enable PCIe pipe_rx_polarity port

Enabled Enabled

Dynamic reconfiguration

Enable dynamic reconfiguration Disabled Disabled

Note: The signals in the left-most column are automatically mapped to a subset of a 128-bit

tx_parallel_data word when the Simplified Interface is enabled.

Related Information

• Using the Cyclone 10 GX Transceiver Native PHY IP Core on page 26

• Bit Mappings When the Simplified Interface Is Disabled on page 143

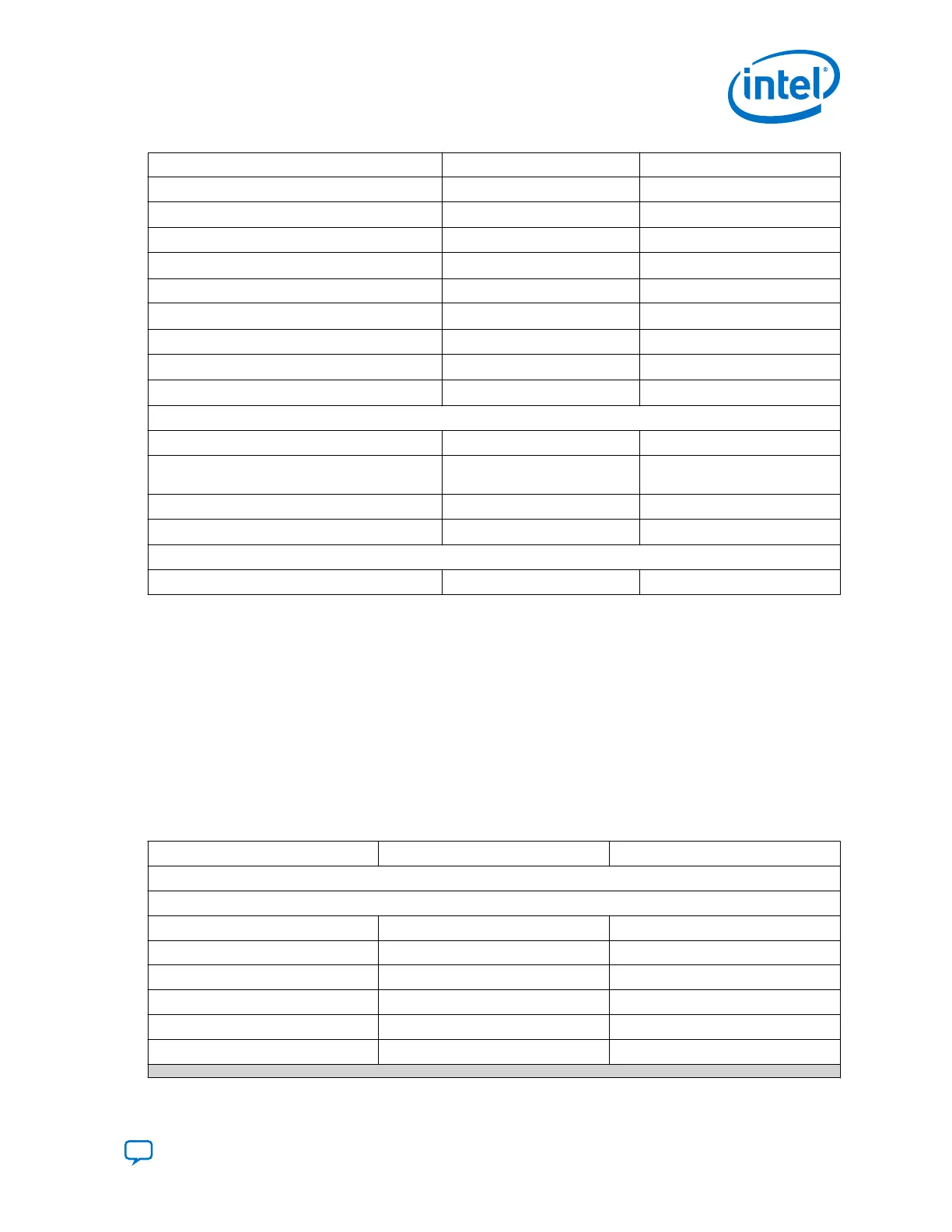

2.7.6. fPLL IP Parameter Core Settings for PIPE

Table 124. Parameter Settings for Cyclone 10 GX fPLL IP core in PIPE Gen1, Gen2 modes

This section contains the recommended parameter values for this protocol. Refer to Using the Cyclone 10 GX

Transceiver Native PHY IP Core for the full range of parameter values.

Parameter

Gen1 PIPE Gen2 PIPE

PLL

General

fPLL mode Transceiver Transceiver

Protocol Mode PCIe Gen 1 PCIe Gen 2

Message level for rule violation Error Error

Number of PLL reference clocks 1 1

Selected reference clock source 0 0

Enable fractional mode Disable Disable

continued...

2. Implementing Protocols in Intel Cyclone 10 GX Transceivers

UG-20070 | 2018.09.24

Send Feedback

Intel

®

Cyclone

®

10 GX Transceiver PHY User Guide

135

Loading...

Loading...