Implementation

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 98

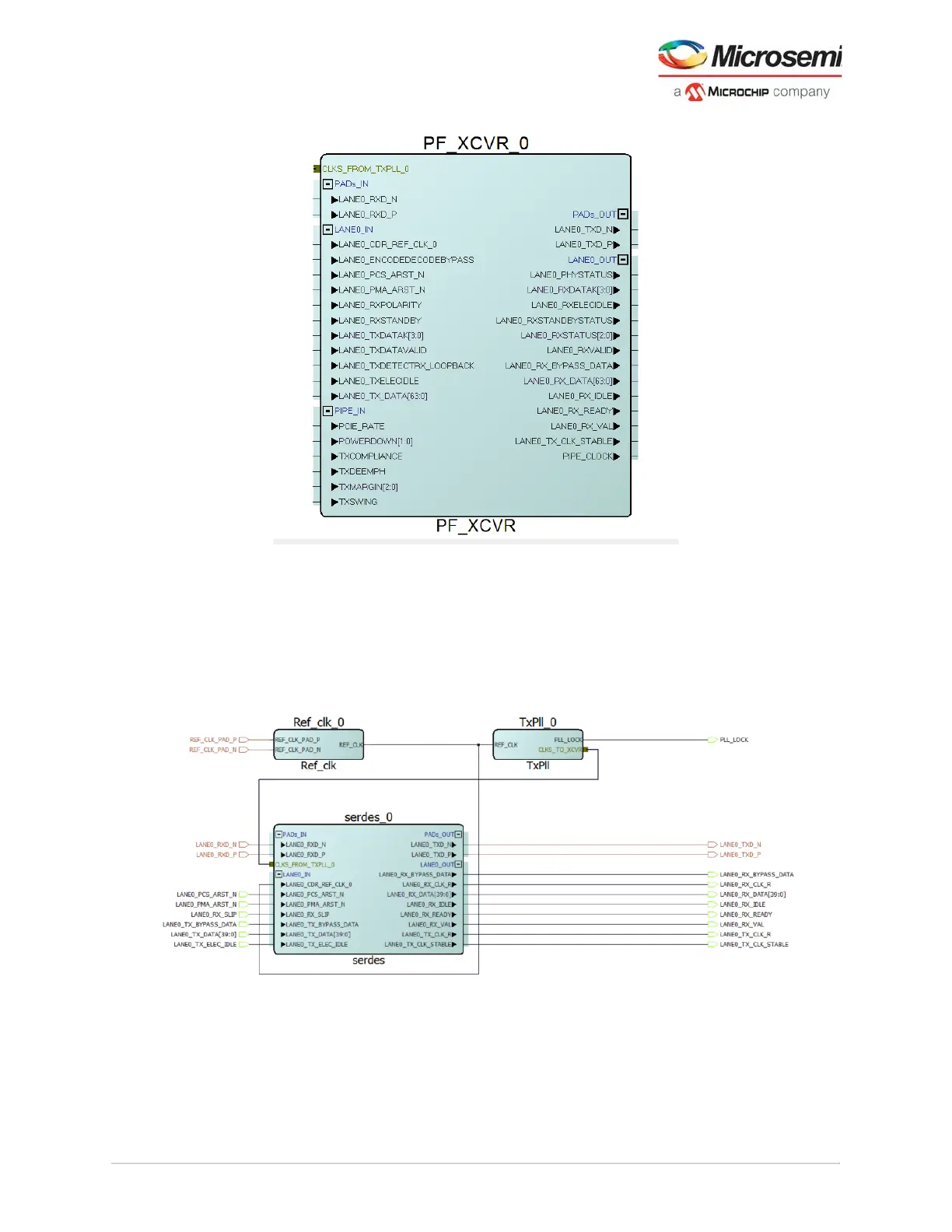

Figure 82 • Soft PIPE PCS Example SmartDesign Component

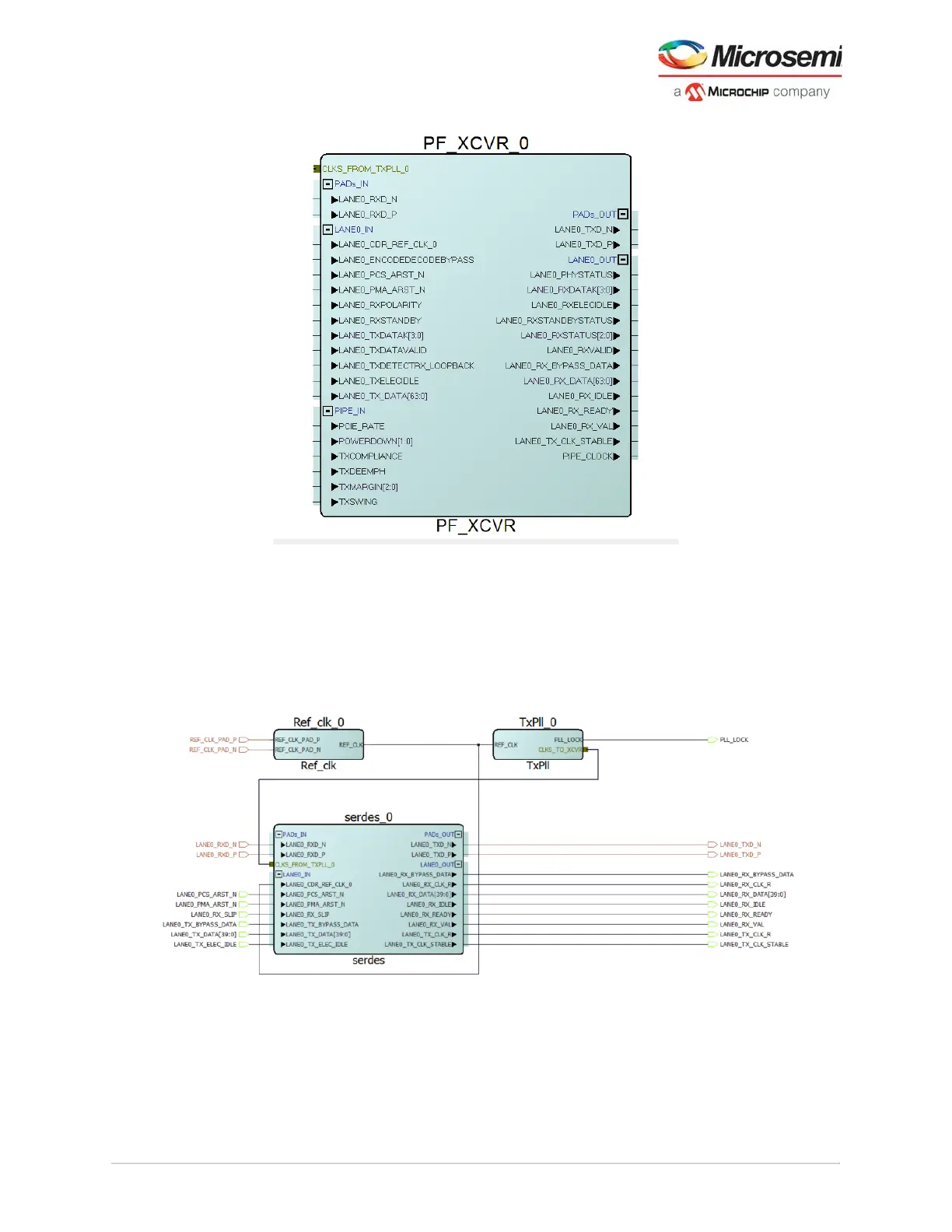

After building the PF_XCVR, PF_TX_PLL and PF_XCVR_REF_CLK cores, the transceiver subsystem

must be connected together in the SmartDesign canvas. Typically, the REF_CLK and/or FAB_REF_CLK

outputs of the PF_XCVR_REF_CLK are connected to the respective inputs of the PF_XCVR and the

input REF_CLK of the PF_TX_PLL. LANE#_TX_PLL_REF_CLK_#, LANE#_TX_BIT_CLK_0, and

LANE#_TX_PLL_LOCK_# are included in CLKS_FROM_TXPLL_# BIF (bus interface). This connection

is required between the TXPLL and transceiver interface. The SmartDesign component must then be

generated.

Figure 83 • Completed Transceiver Subsystem

Loading...

Loading...