Implementation

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 91

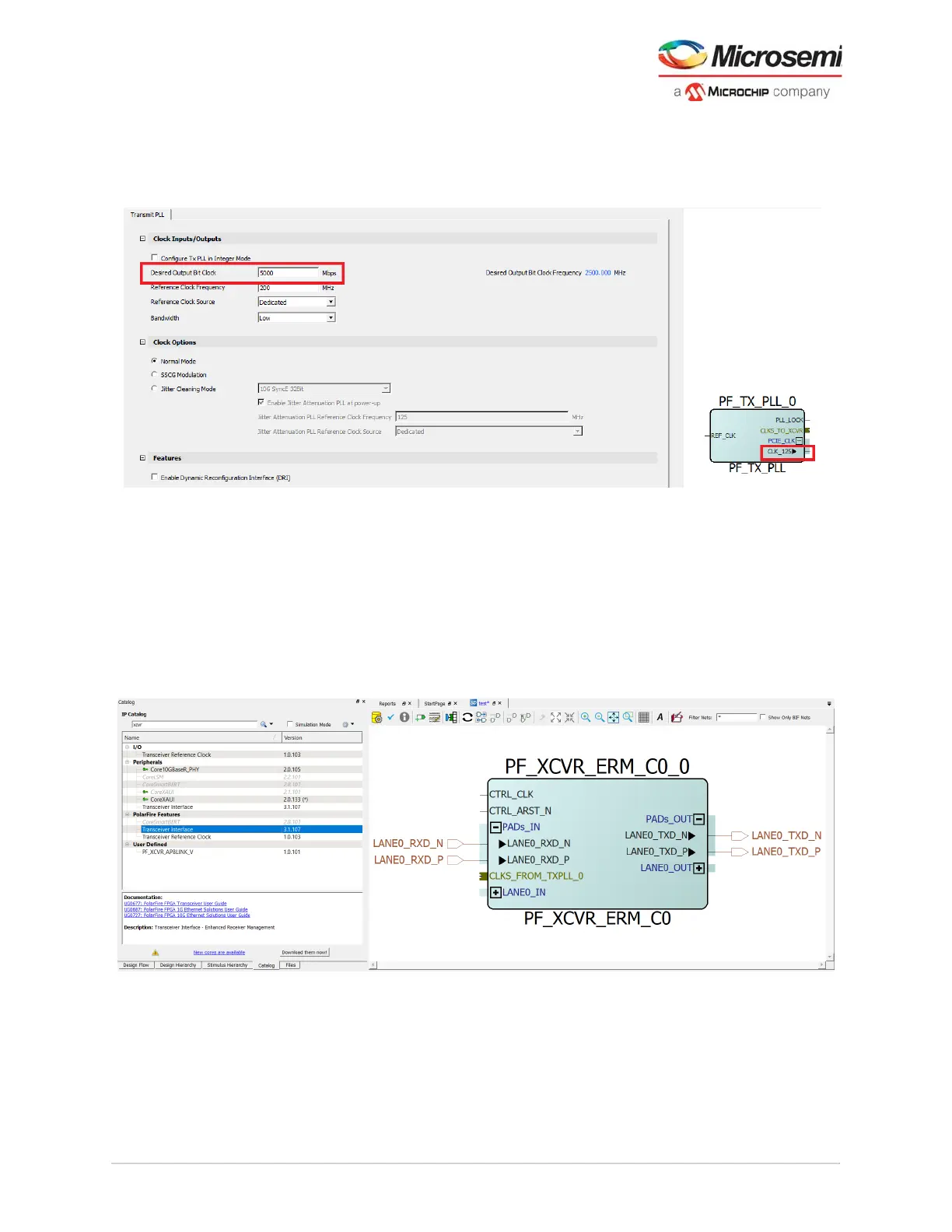

The TxPLL supports an additional clock output. This CLK_125 output port is automatically exposed when

TxPLL BIT_CLK is 5 Gbps. This clock is used with the PCIE macro as input to the transaction layer or

AXI clock. For more information about CLK_125, see UG0685: PolarFire FPGA PCI Express User

Guide.

Figure 71 • CLK_125 GUI

Note: PLL_LOCK port is automatically exposed as an output port on the TXPLL block. It is the PLL lock

indicator signal that can be used to drive logic in the fabric. It is a fabric routed signal.

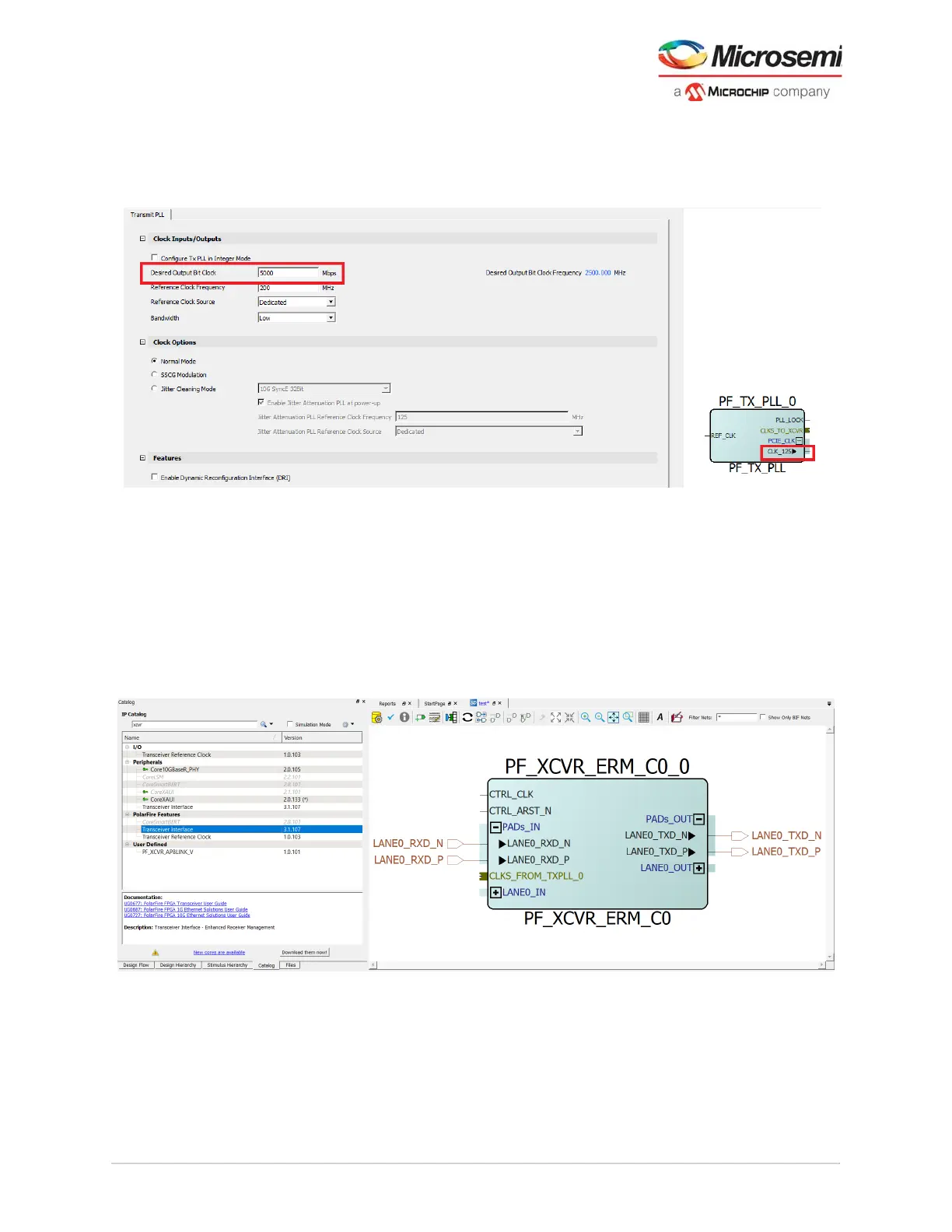

4.1.3 Transceiver Interface Configurator

The Transceiver Interface Configurator is used to build the transceiver based on protocol requirements.

The user selects the number of lanes, data rate, and protocol-specific settings.

To initiate the Transceiver Interface Configurator, perform the following steps:

1. Access the Transceiver Interface module under PolarFire Features from the Catalog window, as

shown in the following figure.

Figure 72 • Transceiver Interface Selection From Catalog

Loading...

Loading...