Functional Description

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 75

3.7 PCS Rate Switch Between 8b10b and 64b66b Mode for

CPRI

All CPRI protocol data rates are statically supported with the Libero Transceiver Configurator using either

8b10b or 64b66b modes. 8b10b supports CPRI rates 2, 3, 4, 5, 6, and 7 while 64b66b mode supports

rates 7a, 8, and 9. In cases requiring dynamic switching, the user must take steps to accommodate the

correct design intentions for switching the PCS mode between the data rates. This case requires a rate

switch between the 8b10b and 64b66b modes.

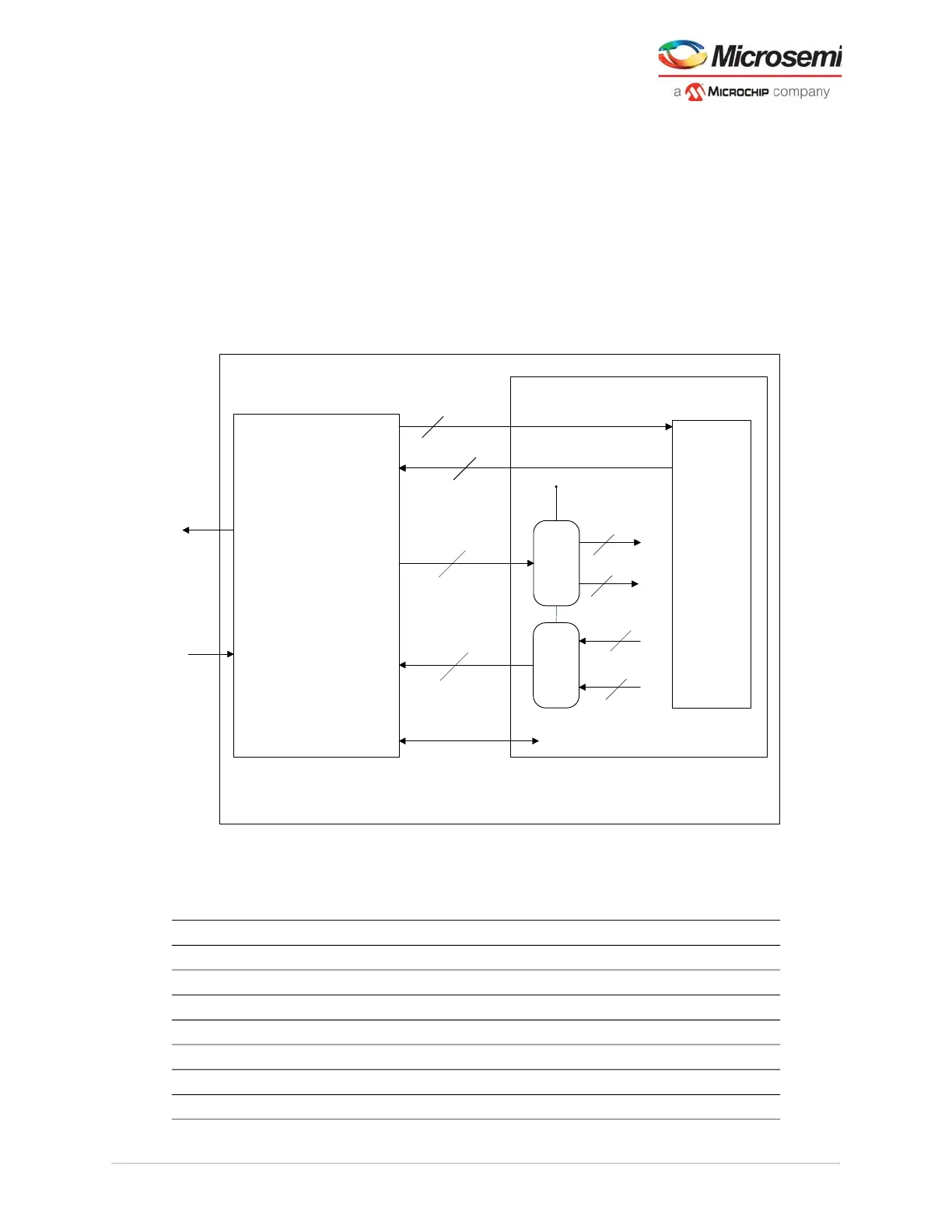

8b10b ports are a superset of 64b66b ports. This implies that the user should plan the FPGA fabric

design to interface with 8b10b ports of the XCVR and use the fabric to control the mode switching to the

CPRI user IP as shown in the following figure.

Figure 55 • PCS Rate Switch between 8b10b and 64b66b Mode

The following table lists the port crossover between the 8b10b and 64b66b modes provided by the XCVR

PCS to the FPGA fabric.

Table 23 • Port Crossover between the 8b10b and 64b66b Modes

DIRECTION 8B10B MODE 64B6xB MODE

Input TX_DISPFNC[15] TX_ELEC_IDLE

Input TX_DISPFNC[14] TX_BYPASS_DATA

Input TX_DISPFNC[13:12] RESERVED_IN[1:0]

Input TX_DISPFNC[11:8] RESERVED_IN[5:2]

Input TX_DISPFNC[7:6] RESERVED_IN[7:6]

Input TX_DISPFNC[5:2] RESERVED_IN[11:8]

Input TX_DISPFNC[1] RESERVED_IN[12]

XCVR PCS

Common

Signals

TXD

RXD

FPGA Fabric

User IP

8b10b

64b66b

8b10b

64b66b

PolarFire

DRI

8b10b

Signals

PCS

Mode

Switch

PCS

Mode

Switch

Switch

Control

Loading...

Loading...