Functional Description

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 49

• Global-Shared: These clocks are similar to Globals but have resources to allow sharing between

the TxPLLs. The sharing of lane clocking resources results in equal latency in the transmitter phase

compensation FIFO of all shared lanes.

Note: Global-Shared mode allows the global clock output from one lane to be used for other lanes. This

clocking mode is used when several lanes are part of the same protocol using the same clock.

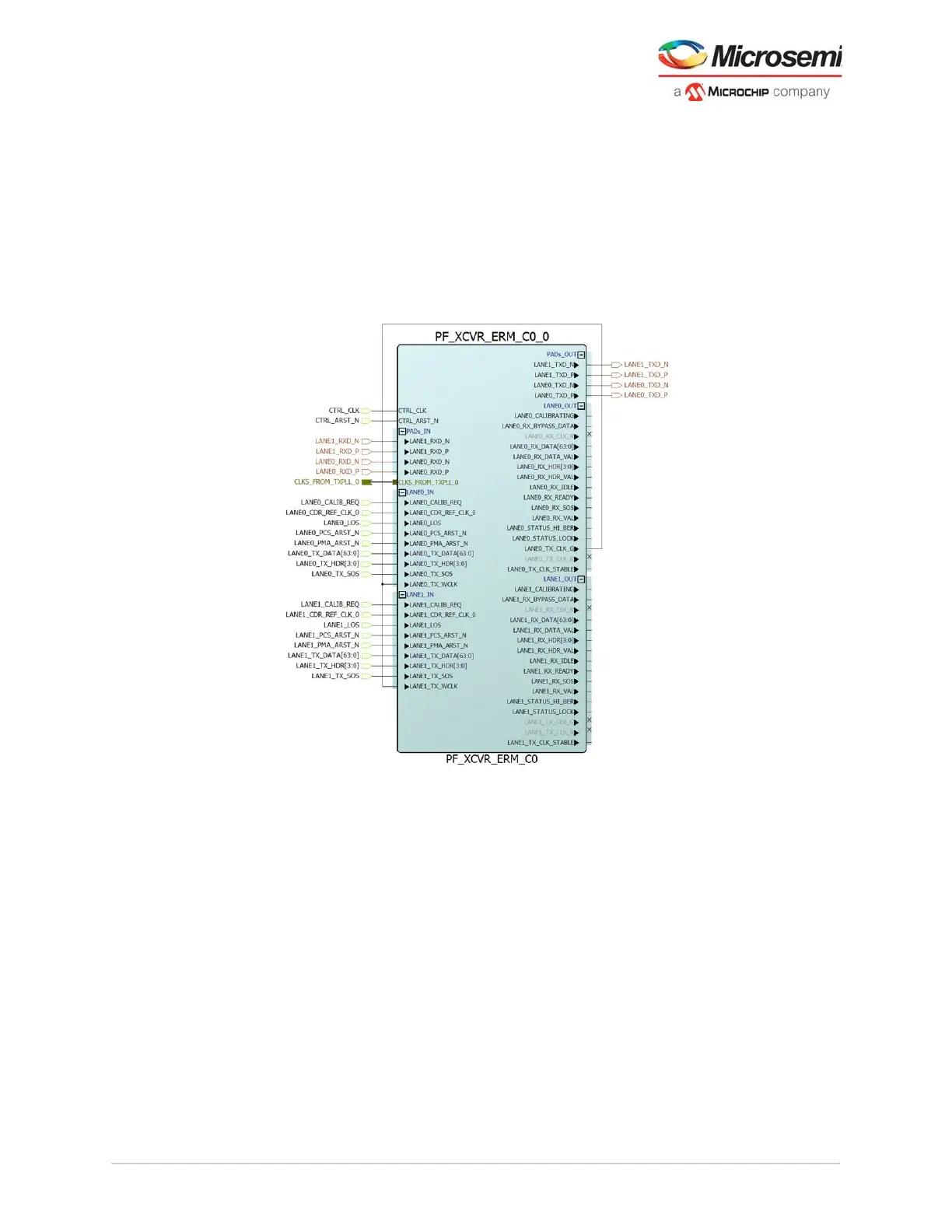

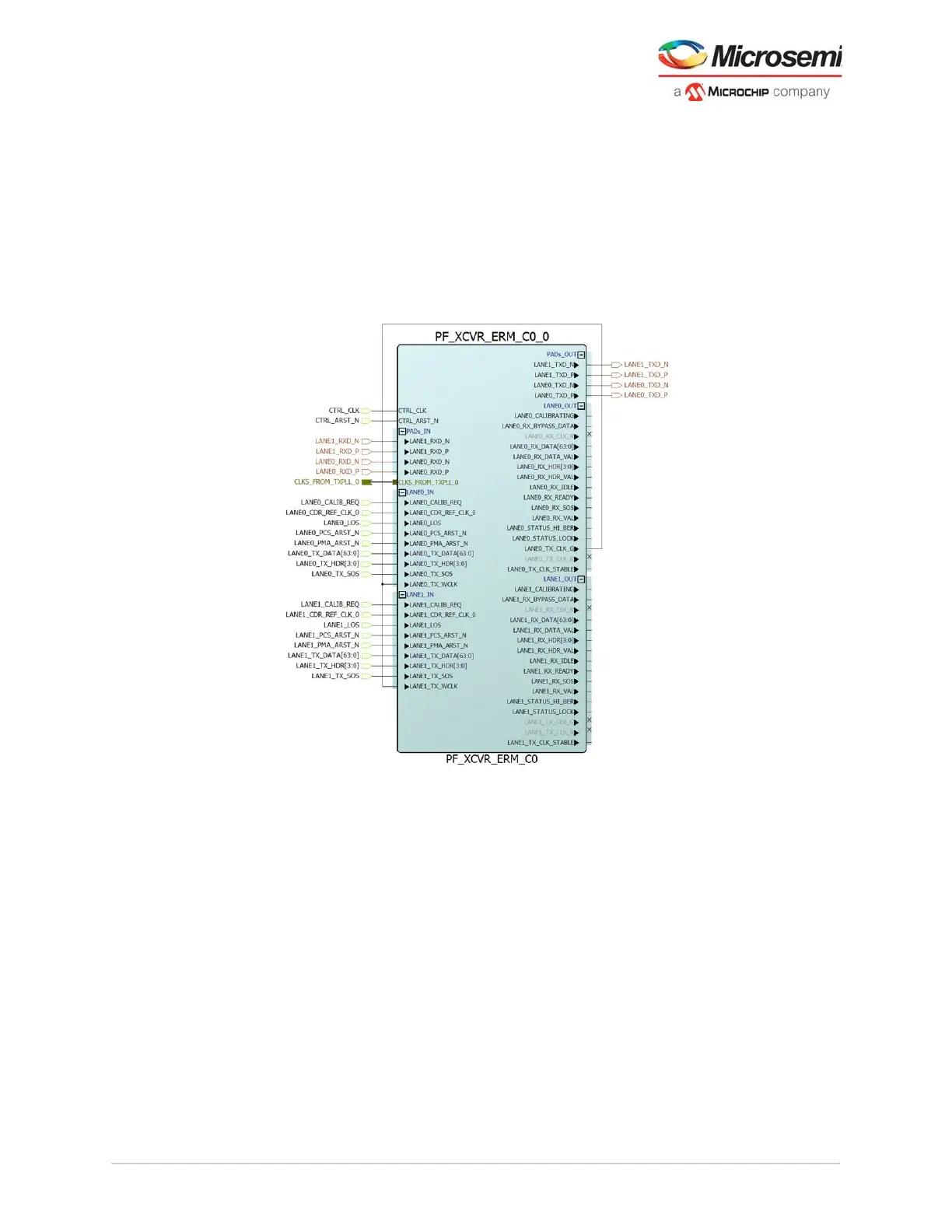

When Global-Shared mode is enabled, all the lanes include a global clock output port, but only one lane

can be used as the master port. All the lanes include a TX_WCLK input port. This port must be

connected to the global clock output of the master lane. The fly-wheel FIFO absorbs the phase difference

between the lanes and the master lane’s global clock. See the following SmartDesign figure for an

example.

Figure 30 • Global-shared Clocking Example

• Regional: These clocks use local resources to interconnect with the FPGA fabric with a FIFO in the

data path at the fabric boundary.

• Regional (Deterministic): These clocks use local resources to interconnect with the FPGA fabric

with zero-cycle data path at the fabric boundary providing low-latency.

Microsemi IP and solutions use these resources to optimize the FPGA architecture to provide robust use

cases. See Table 16, page 54.

3.4.1 Non-Deterministic Interface

The transceiver PMA to FPGA fabric/PCS data path includes a flywheel FIFO (FWF) interface, which is

used to transfer data between clock domains. This interface is included within the protocol-specific PCS

HDL modules or user FPGA fabric logic.

FWF is a simple form of FIFO where its write and read clocks are known to be at the same nominal

frequency, with some allowed phase difference and jitter that is compensated within the block.

The interface between the PMA and fabric cannot be throttled. However, the addition of the FWF block in

the data path handles the phase crossing of every PMA lane, ensuring that timing is met across this

interface. The received data, along with the recovered parallel clock, is passed to the FWF, which

synchronizes the data and clock for either regional or global clock routing.

Loading...

Loading...