Overview

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 5

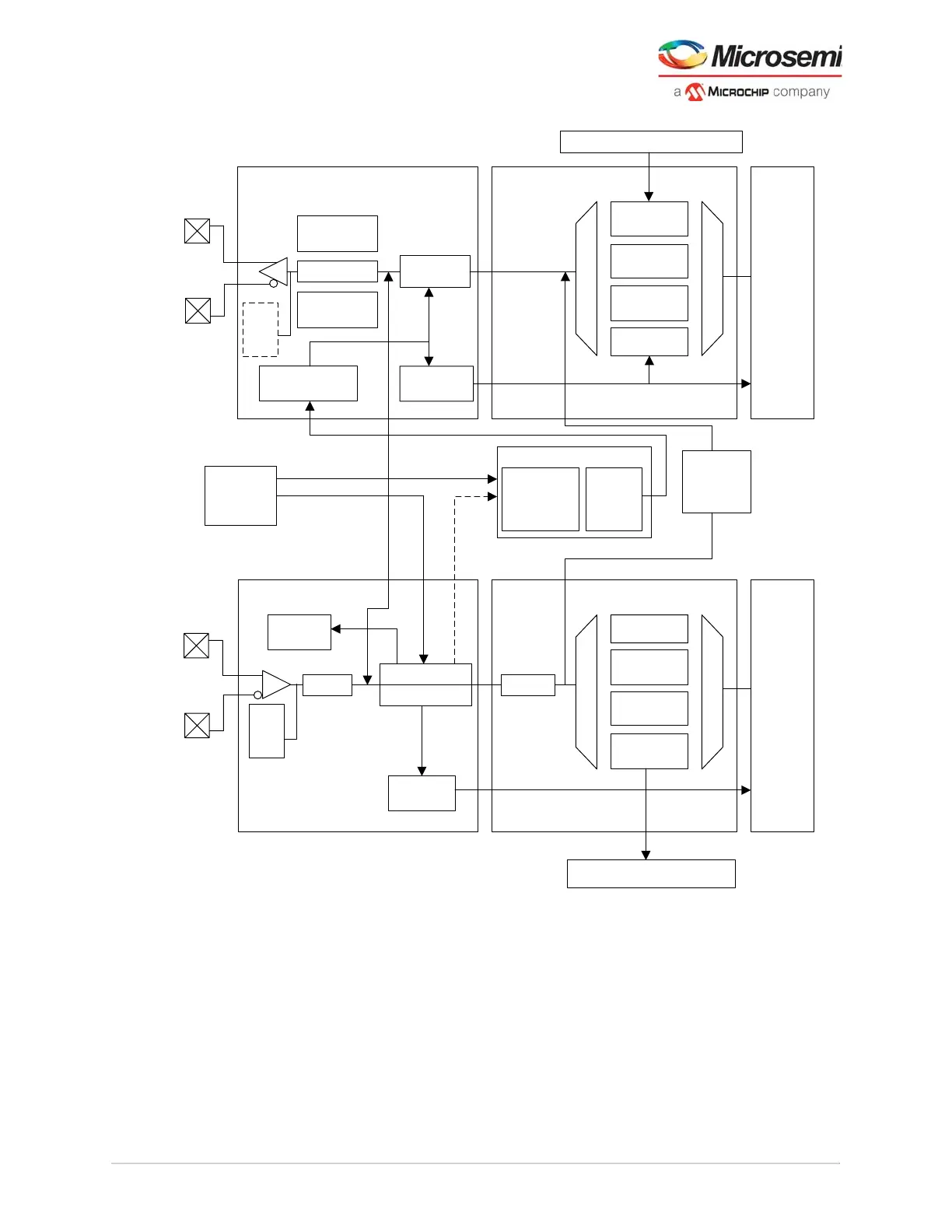

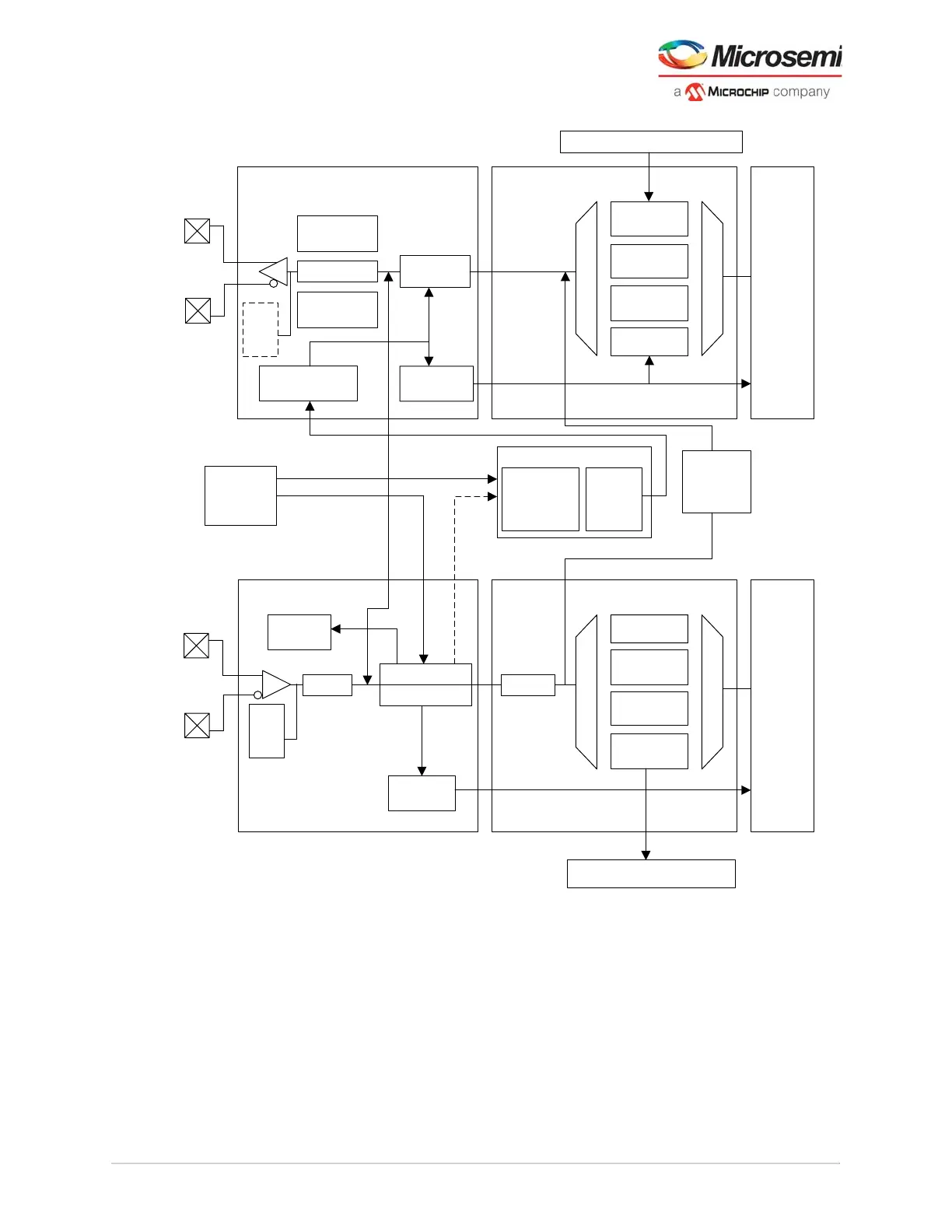

Figure 1 • Transceiver Lane Overview

Note: Transmit/receive fabric interfaces are specified in the associated PCS pin lists, that is, 8b10b, 64b6xb,

PIPE, and PMA Only.

Note: For more information on PCIe Sub-system, see UG0685: PolarFire FPGA PCI Express User Guide.

Transmit

PCS/

Fabric

Interface

Transmit PMA

PCIe Sub-System (PCIESS)

Transmit PCS

Receive

PMA

Transmit PLL

Reference

Clock

Network

Receive

PCS

Polarity

Receive

PCS/

Fabric

Interface

PCIe Sub-System (PCIESS)

8b10b

Encoder

64b/6xb

Encoder

PCIe/PIPE

Pre-/Post-

Emphasis

Serializer

PCS

Divider

Out of Band

Electrical

Idle

PMA Only

CTLE

Eye

Monitor

Jitter

Attenuation

or Spread

Spectrum

Frac-N

PLL

8b10b

Decoder

64b/6xb

Decoder

PCIe/PIPE

PMA Only

PCS

Divider

÷ 1, 2, 4, 8, 11

CDR w/DFE

Deserializer

Loopback

FIFO

XCVR_TXP

XCVR_TXN

XCVR_RXP

XCVR_RXN

CTLE: Continuous Time Linear Equalization

DFE: Decision-feedback Equalizer

Optional path used

with Jitter

Attenuation

EQ Far_end Loopback or

Near-End Loopback

CDR Far-End

Loopback

PCIe

Rx

Det

LOS

Det

Loading...

Loading...