Functional Description

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 65

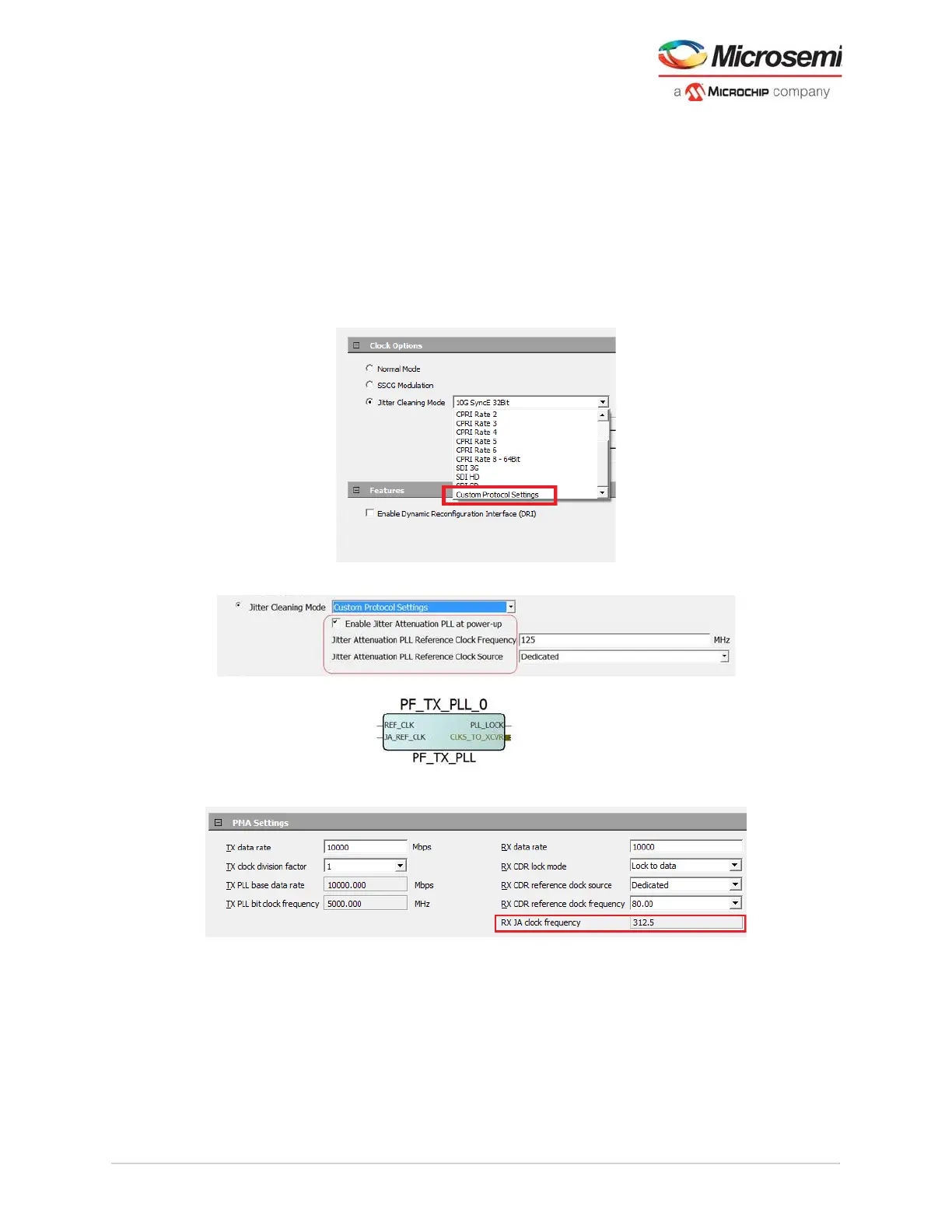

3.5.4.2.1 Custom Protocol Settings

Full duplex jitter attenuation solution is available for custom protocols in Libero SoC v12.3 or later. This

support is for one refclk and one data rate allowing user the flexibility to create designs requiring

customized settings not already supported by the presets.

The user must enter the reference clock frequency and clock source information for the correct

generation of the jitter cleaning configuration. The reference clock source selection determines the input

clock ports exposed on the component (See Figure 47, page 65). Users are required to connect the ports

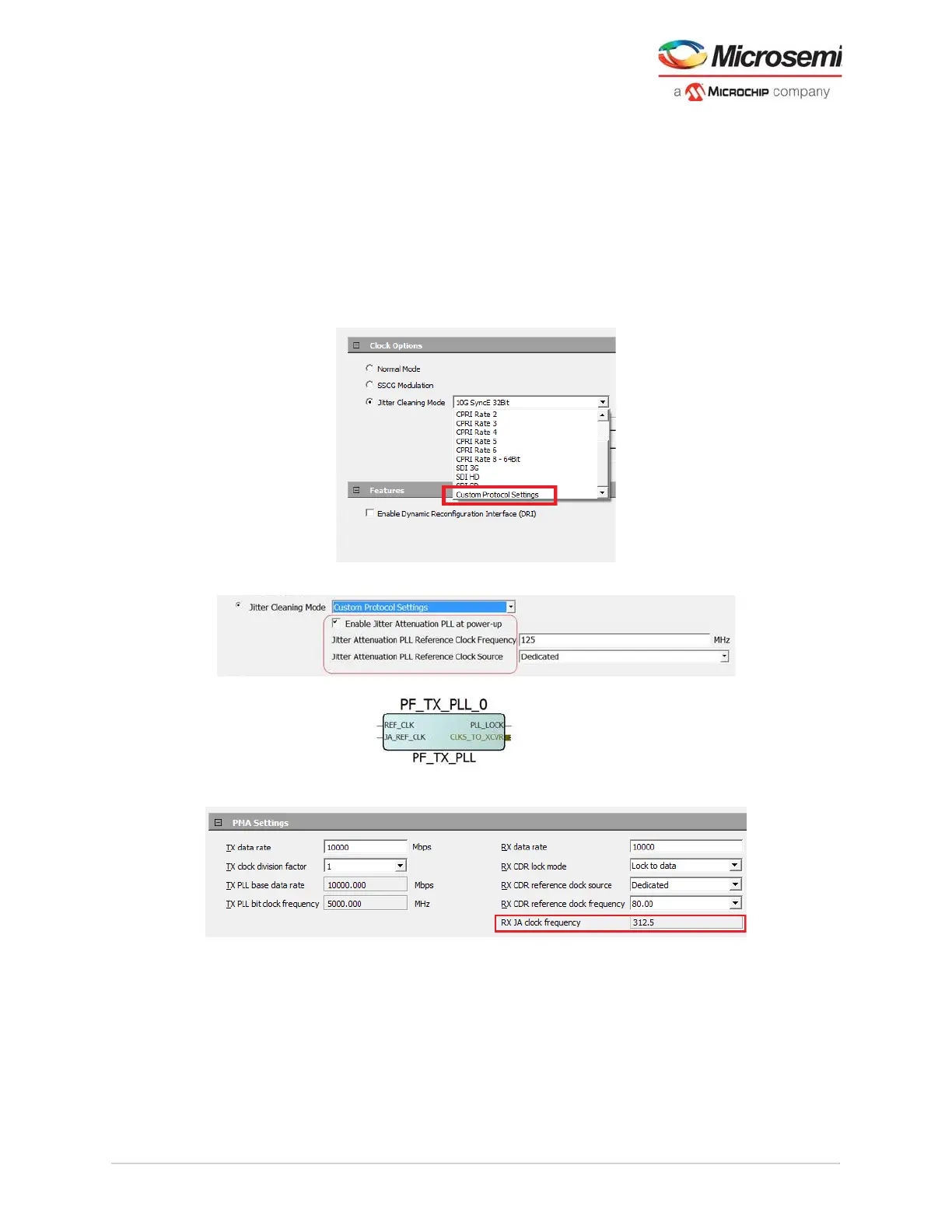

in the top level to the correct XCVR lane. The use of the JAPLL with custom settings require the user to

use the JA clock frequency for the associated lane as it appears in the RX JA clock frequency dialogue

box of the XCVR configurator (See Figure 48, page 65).

Figure 46 • JAPLL Custom Protocol Setting

Figure 47 • Reference Clock Source Options

Figure 48 • Rx JA Clock Frequency (XCVR Configurator)

Loading...

Loading...