Functional Description

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 35

3.3.2.5 64b67b Transmit

In the recommended configuration for 64b67b, encoded and scrambled data is presented from the fabric

into TX_DATA along with sync headers on TX_HDR[3:0]. The data from the fabric must conform to the

expected sequence of clock beats according to the fabric interface width.

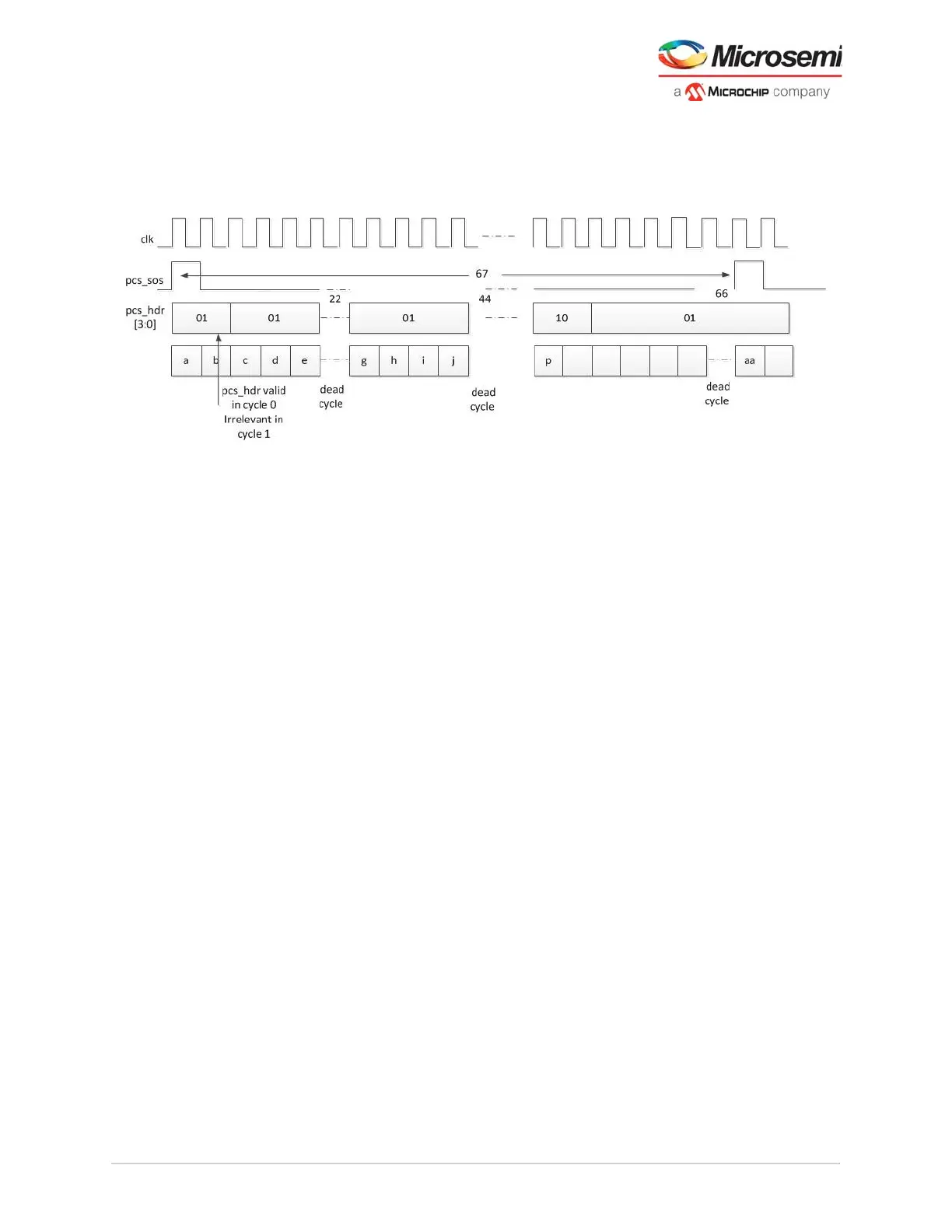

Figure 22 • 64b67b Transmit Sequence For 32-Bit Interface

The 64-bit interface option has dead cycles on clock beats 44, 45, 88, 89, 132 and 133.

The transmit data first enters the PCS Timing control block, which generates the appropriate markers for

64b67b blocks. The data then goes to the disparity calculation block. The total number of ones and zeros

are balanced by inverting blocks as necessary. When a block is inverted, sync header bit 2 is set to mark

the inversion. Bits [1:0] of the sync header have the same meaning as they do in 64b66b blocks.

Data from the disparity block then goes to the transmit gearbox where it is output in 32-bit chunks per

clock beat and sent to the PMA serializer.

3.3.2.6 64b67b Receive

Data comes into the 64b67b receiver from the PMA 32-bits per clock beat from the de-serializer. The

data is qualified by RX_READY=1, which is set by the greater PMA logic when CDR achieves bit lock

and is producing a stable clock.

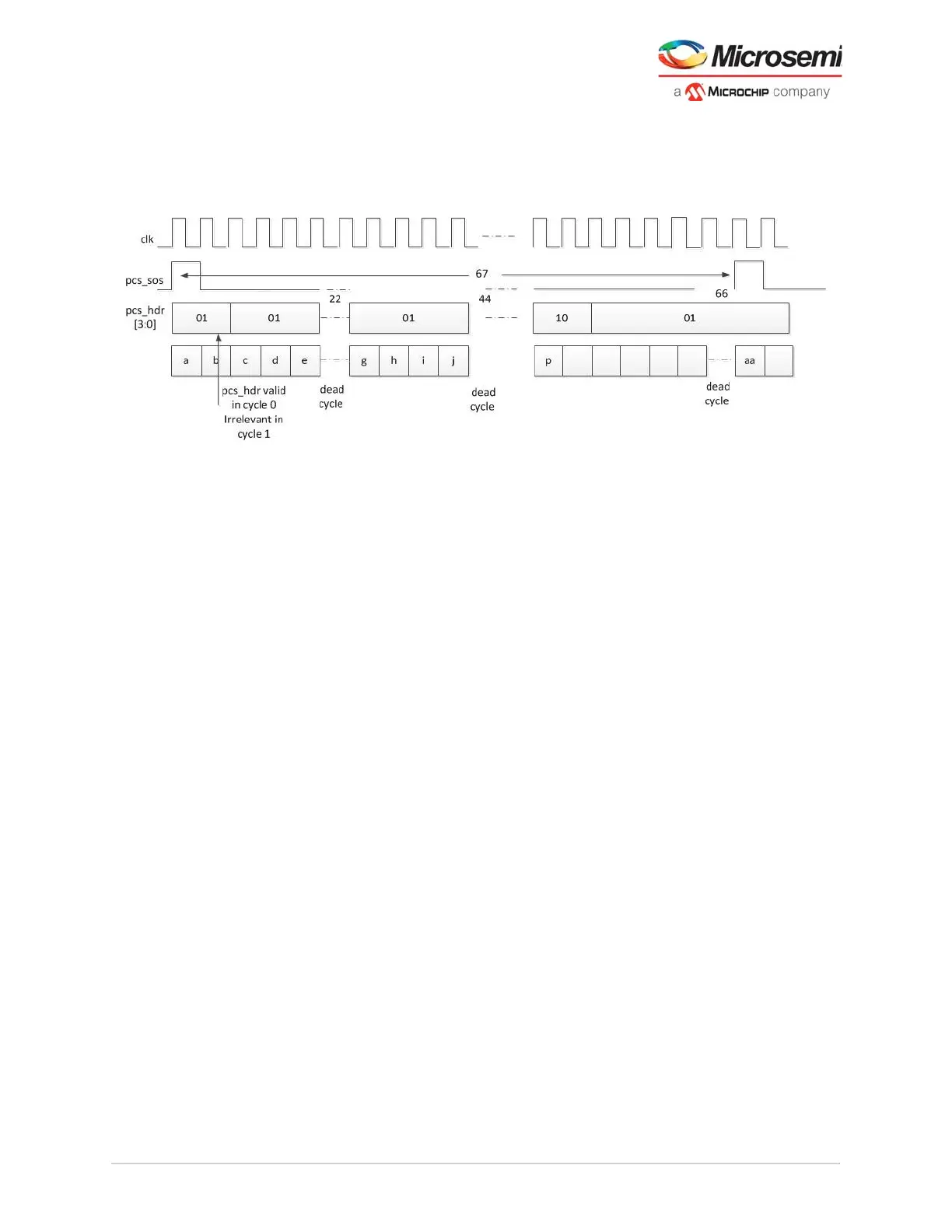

The receive gearbox frames the 67-bit blocks by examining sync header bits [1:0] in the same method as

described for 64b66b. The difference is in the span of bits between sync headers. The receive disparity

block invert blocks as indicated by sync header bit [2]. The receive data is then sent to the fabric in 64-bit

or 32-bit clock beat sequences. The 32-bit sequence is shown in the following figure where two clock

beats transfer one symbol. In the 32-bit width, the sequence is 134 clock beats long and contains blank

symbol transfers for clock beats 44-45, 88-89 and 132-133.

Loading...

Loading...