Implementation

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 102

create_clock -period <T> [get_pins {LANE<n>/RX_CLK_R}]

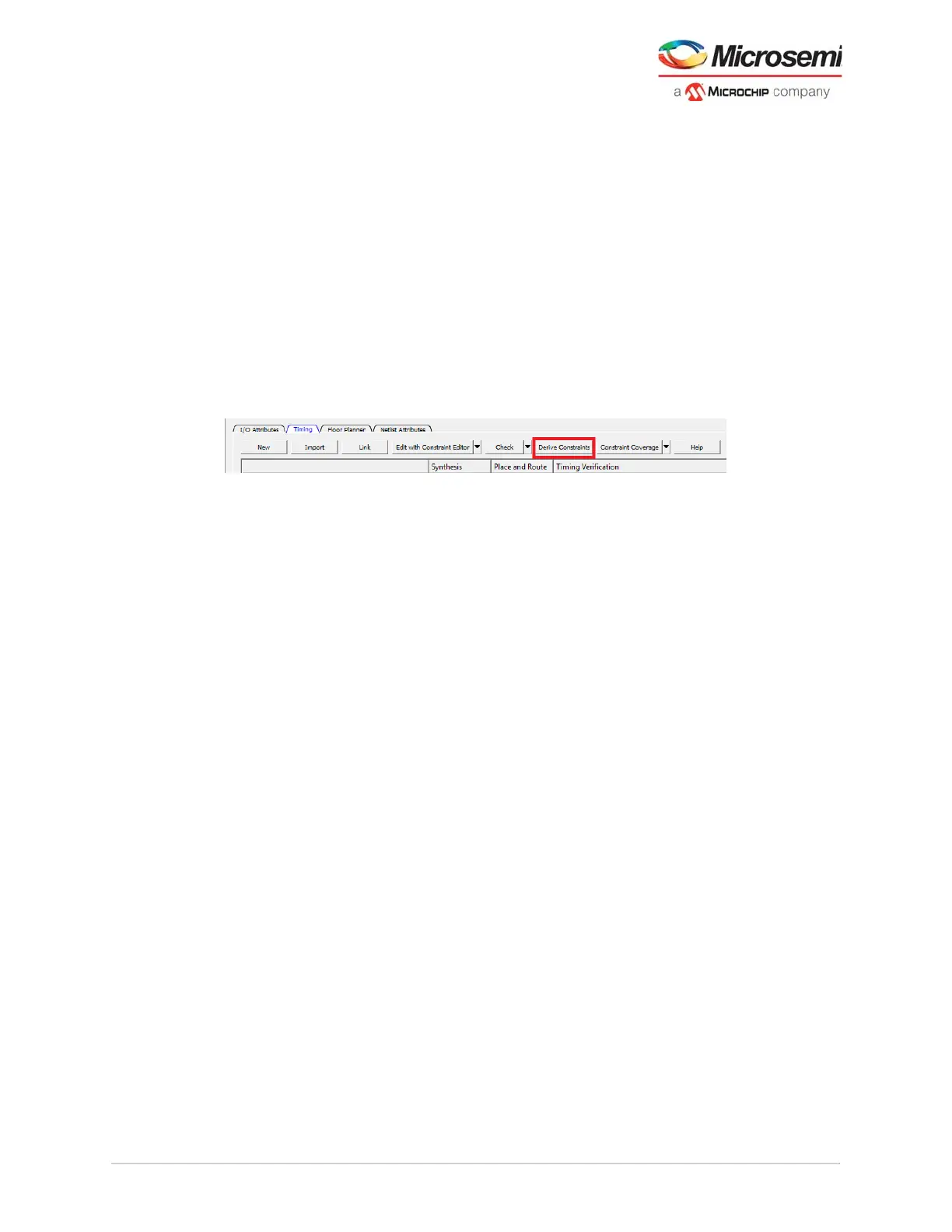

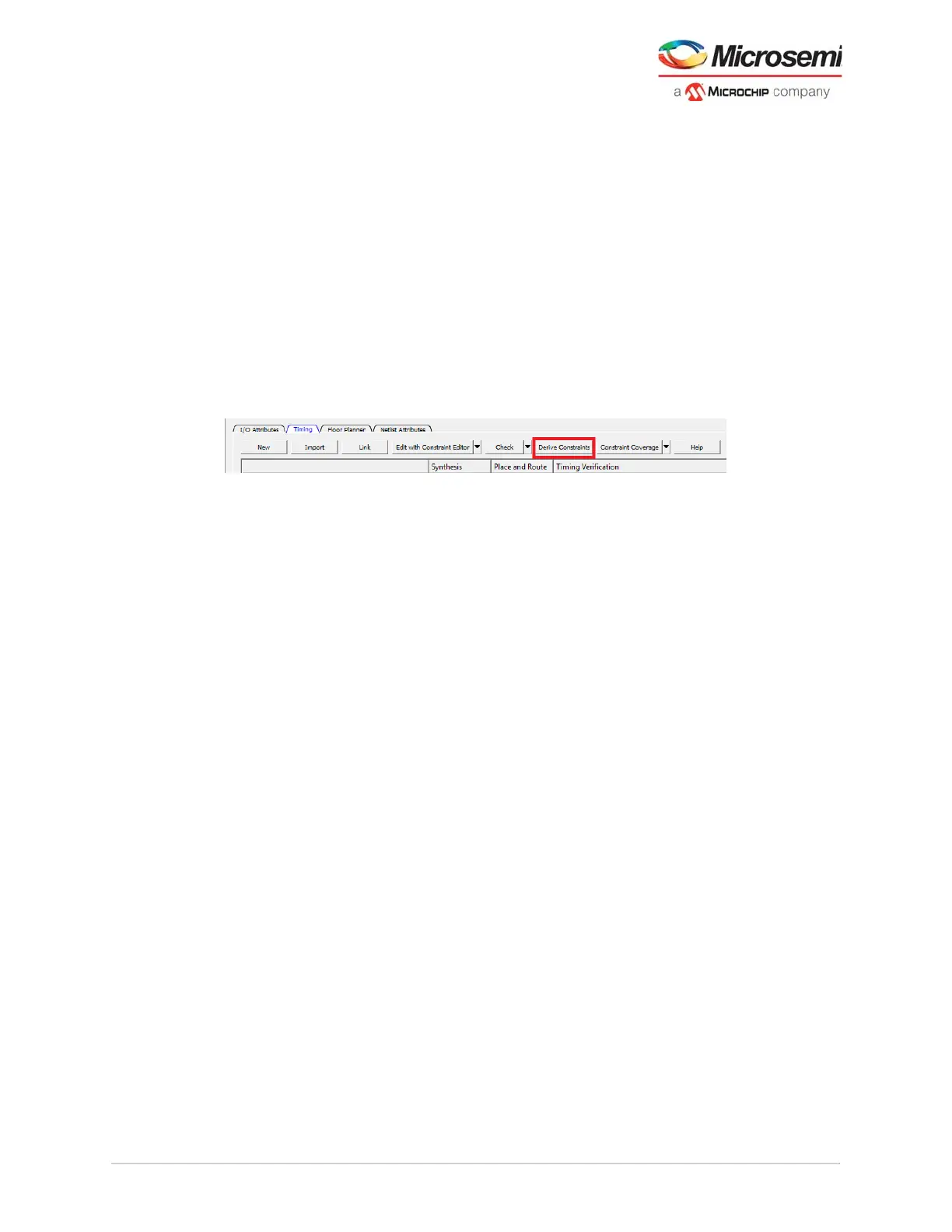

Users need to use the Derived SDC file generated by clicking the Derive Constraints in the Timing tab

of the Constraint Manager window of Libero SoC software.

The following example shows a Libero project with transceiver.

create_clock -name {REF_CLK_PAD_P} -period 6.4 [ get_ports { REF_CLK_PAD_P }

]

create_clock -name {My_Project_0/my_xcvr_0/PF_XCVR_0/LANE0/TX_CLK_R} -period

16 [ get_pins { My_Project_0/my_xcvr_0/PF_XCVR_0/LANE0/TX_CLK_R } ]

create_clock -name {My_Project_0/my_xcvr_0/PF_XCVR_0/LANE0/RX_CLK_R} -period

16 [ get_pins { My_Project_0/my_xcvr_0/PF_XCVR_0/LANE0/RX_CLK_R } ]

create_clock -name

{My_Project_0/my_pll_0_0/pll_xvier_0_0/txpll_isnt_0/DIV_CLK} -period 8 [

get_pins { My_Project_0/my_pll_0_0/my_pll_0_0/txpll

Figure 86 • Derive Constraints using Constraints Editor

The PolarFire transceiver can source three different clocks into the fabric—TX_CLK, RX_CLK, and the

REFCLK (FAB_REF_CLK). These clocks contain high frequency jitter that is not reported by Libero in the

timing report and SmartTime. It is recommended that users add clock uncertainty constraints to these

clocks in their design.

The following is a list of recommended values for clock uncertainty per clock, resource, and speed-grade.

FAB_REF_CLK on Global: 275ps for STD, 200ps for -1

FAB_REF_CLK on Regional: Not supported

TX_CLK_G on Global: 300ps for STD, 225ps for -1

TX_CLK_R on Regional: 225ps for STD, 150ps for -1

RX_CLK_G on Global: 325ps for STD, 250ps for -1

RX_CLK_R on Regional: 250ps for STD, 175ps for -1

Following is an example clock uncertainty constraint. This constraint would be added to the user's timing

SDC file.

# TX_CLK and RX_CLK on Regionals

set_clock_uncertainty -setup 0.150 [ get_pins {

PF_XCVR_ERM_LANE2/I_XCVR/LANE0/TX_CLK_R } ]

set_clock_uncertainty -setup 0.175 [ get_pins {

PF_XCVR_ERM_LANE2/I_XCVR/LANE0/RX_CLK_R } ]

# TX_CLK and RX_CLK on Globals

set_clock_uncertainty -setup 0.300 [ get_pins {

PF_XCVR_ERM_LANE2/I_XCVR/LANE0/TX_CLK_G } ]

set_clock_uncertainty -setup 0.325 [ get_pins {

PF_XCVR_ERM_LANE2/I_XCVR/LANE0/RX_CLK_G } ]

# FAB_REF_CLK on Global

set_clock_uncertainty -setup 0.275 [ get_clocks REF_CLK_PAD_P ]

Loading...

Loading...