Board Design Recommendations

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 127

8.2 Design for Protocols

Transceiver designs are used in many high-speed protocols. Each protocol specifies the system

requirements to meet the specific standards of the protocol. The electrical performance requirements for

these protocols must be addressed by proper design of the PCB. The following sections describes the

PCB requirements of PolarFire transceivers for specific protocols. For more information, see UG0726:

PolarFire FPGA Board Design User Guide.

8.2.1 PCI Express

PCIe is a point-to-point serial differential low-voltage interconnect supporting up to four channels. Each

lane consists of two pairs of differential signals: a transmit pair, XCVR_x_TXy_P/N, and a receive pair,

XCVR_x_RXy_P/N. Each signal has a 2.5 GHz embedded clock.

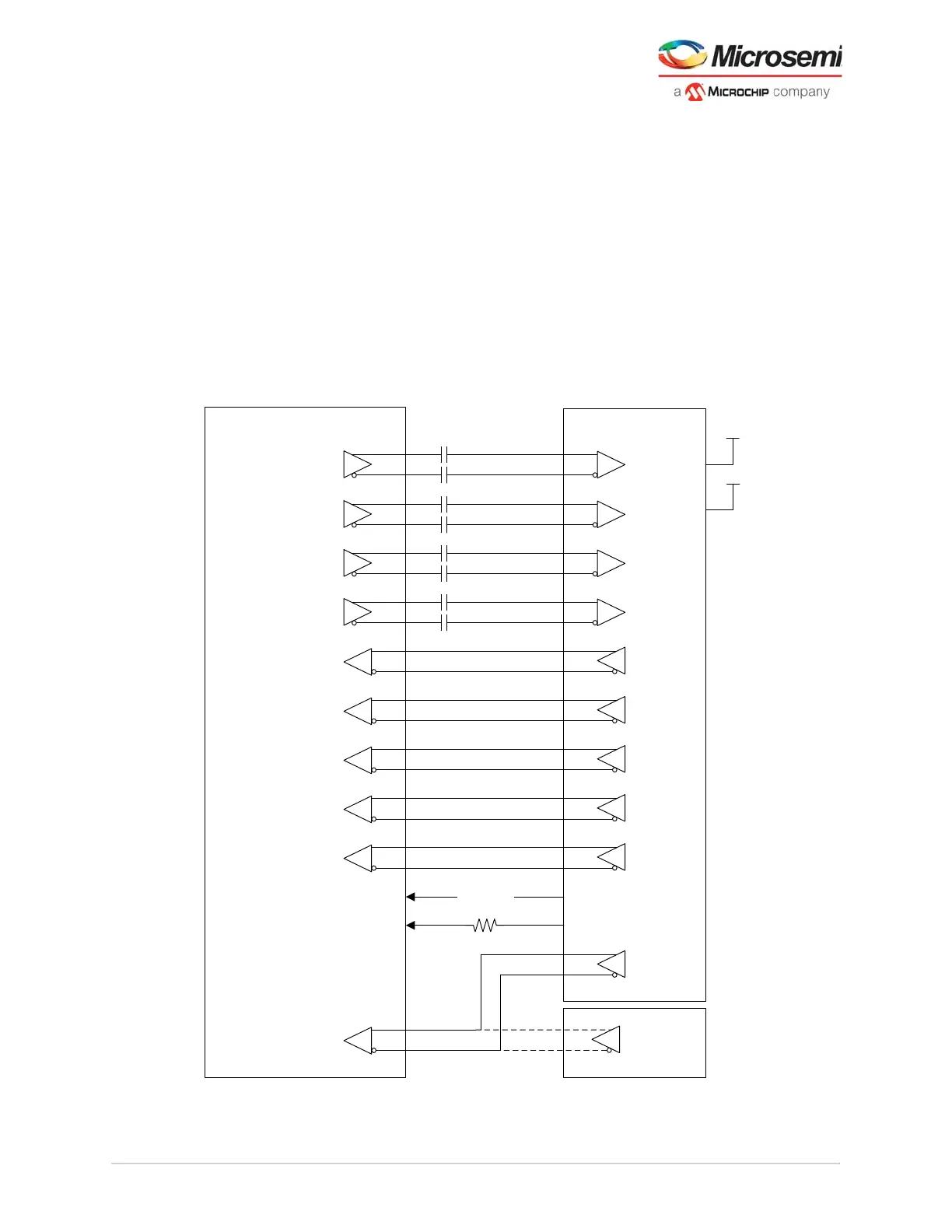

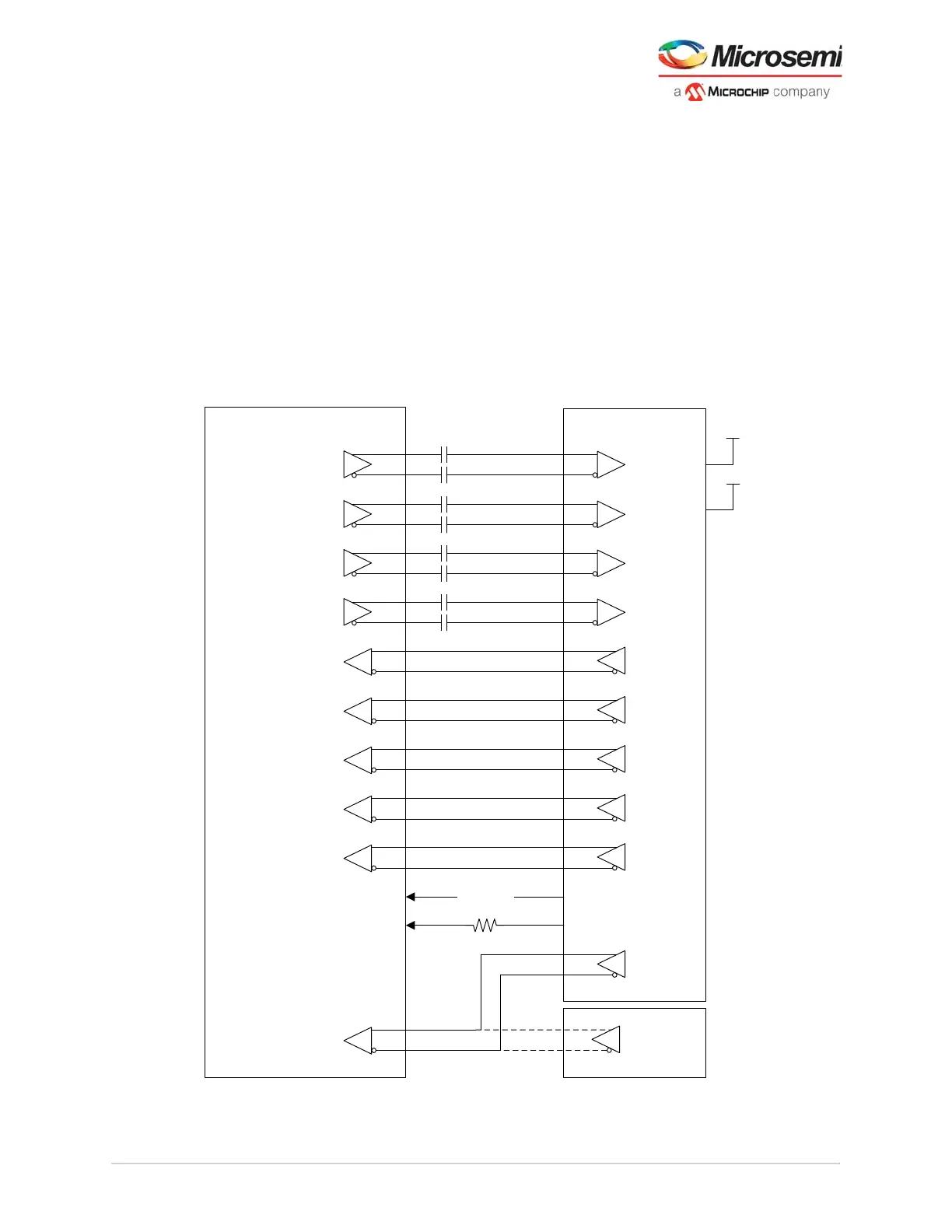

The following figure shows the connectivity between the PolarFire FPGA transceiver interface and the

PCIe edge connector.

Figure 102 • Connectivity Between XCVR Interface and PCIe Edge Connector

XCVR Interface

PCIe Edge

Connector

Tx Rx

0.1 μF

0.1 μF

XCVR Lane0/TXD

Tx Rx

0.1 μF

0.1 μF

XCVR Lane0/TXD

Tx Rx

0.1 μF

0.1 μF

XCVR Lane1/TXD

Tx Rx

0.1 μF

0.1 μF

XCVR Lane2/TXD

Rx

Tx

XCVR Lane0/RXD

Rx

Tx

XCVR Lane1/RXD

Rx

Tx

XCVR Lane2/RXD

Rx

Tx

XCVR Lane3/RXD

Rx

Tx

XCVR REFCLK0

Reset#

ƻRSWLRQDO

)DEULF,2

)DEULF,2

Wake#

Rx

Tx

Tx

2QERDUG

100 MHz

GLIIHUHQWLDO

FORFNVRXUFH

XCVR REFCLK1

+12 V

+3.3 V

Loading...

Loading...