Functional Description

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 21

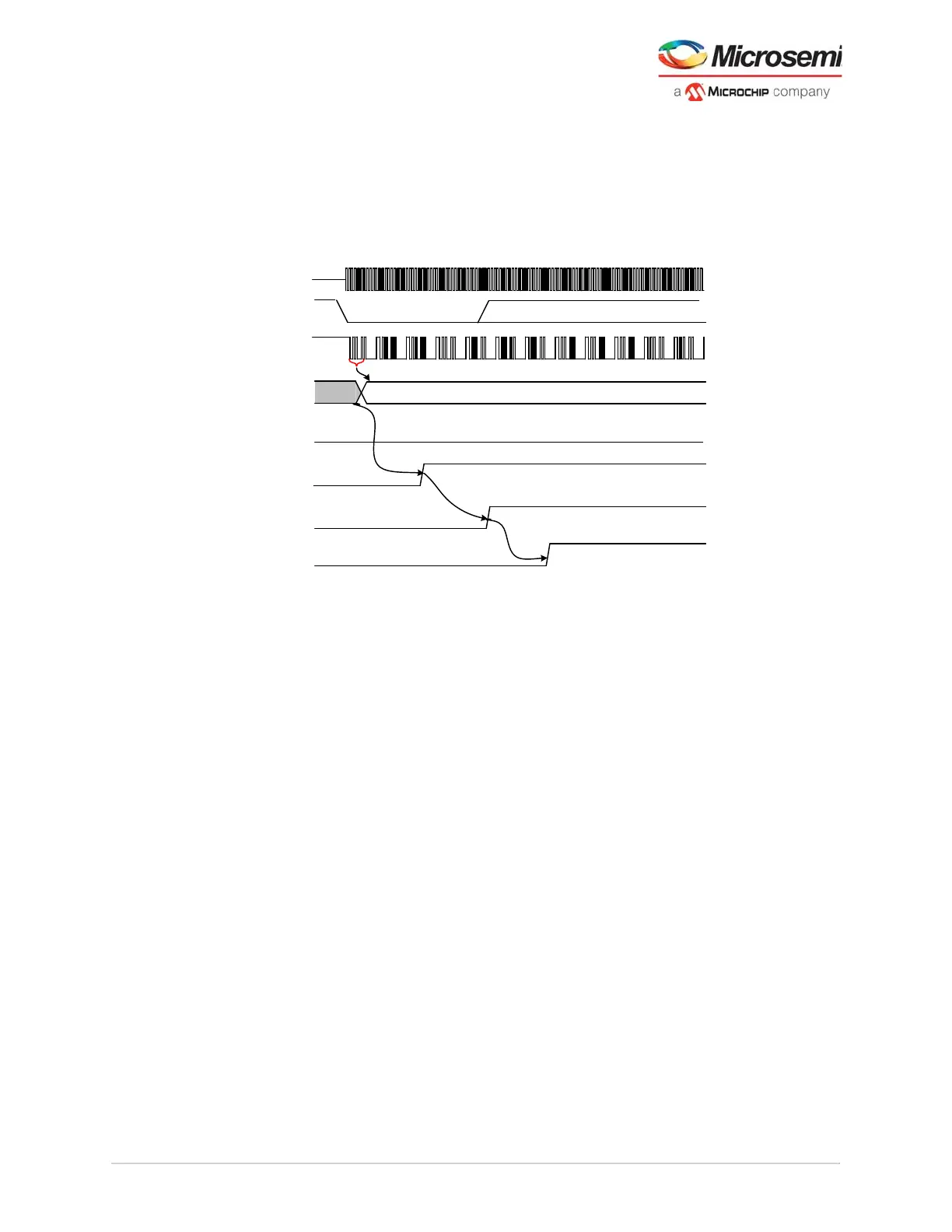

The ERM manages the re-establishment of a link after a break or disruption. A restart begins when a

valid data stream is re-applied to the receiver inputs. This starts the operation of the ERM to

systematically control the CDR to re-initialize the link. As shown in following figure, the ERM properly re-

establishes a CDR fine lock after assuring the link is stable. When the link polling is complete, the ERM

transitions the transceiver back to proper operation. This is completed without changing any of the CDR

or DFE calibration settings and returns calibration setting to those used prior to the disruption or break in

the serial data stream.

Figure 14 • Restart after Initialization

Note: RX_IDLE integrator detects threshold for signal-presence.

The user also can optionally invoke a calibration on-demand. This would be needed if the interconnection

is changed such as swapping cables or other interface media. In this case, the user can request

calibration only after a valid data stream is applied to the RXD inputs. As shown in following figure,

assertion of the LANE#_CALIB_REQ initiates the ERM to invoke a CDR/DFE calibration during which

the CDR remains LOCK2DATA. The LANE#_CALIB_REQ is required to stay asserted by the user logic

until LANE#_CALIBRATING goes high.

LTR

Glitches on RX_IDLE is expected for incoming traffic > 5Gbps

LANE#_RXD[P-N]

LANE#_RX_IDLE

CDR Status(Internal)

LANE#_CALIBRATING

LANE#_RX_VAL

LTR= Lock to Reference clock

LTD= Lock to Data

LTD

See note

LANE#_RX_READY_CDR

LANE#_RX_READY

(Rx Fine Lock)

LANE#_LOS

Do Not Care

Loading...

Loading...