Functional Description

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 31

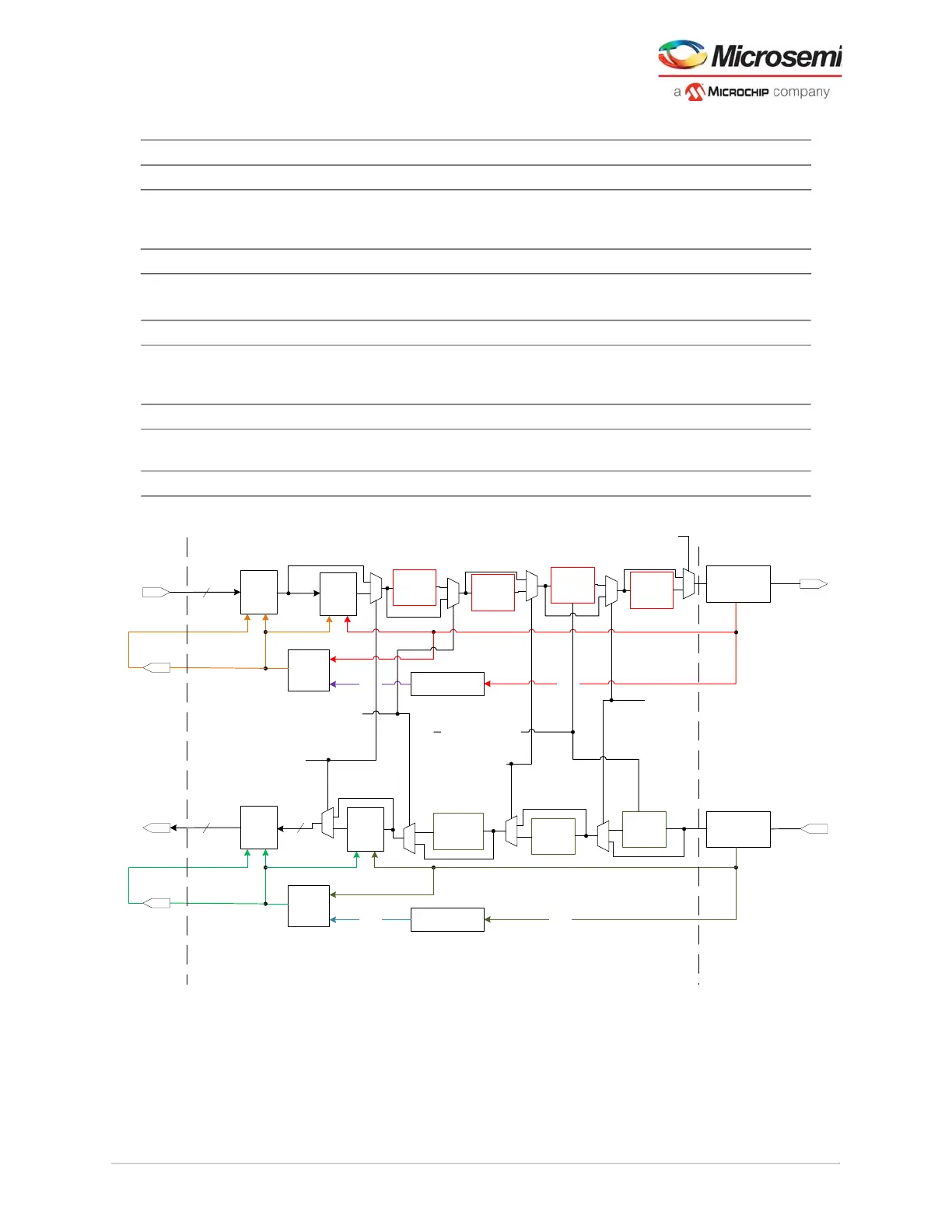

Figure 17 • 64b6xb Data Path

Tx Disparity Implements inversion of 67-bit symbol. Only for use in Interlaken.

Tx Gearbox Outputs continuous stream of 32-bits per clock beat to the PMA given an input consisting

of 64-bit block symbols, which has cyclic gaps in its active clock beats. This block inserts

the 2 or 3 bits of header on each block.

Tx Test Gen Optionally replaces the output stream with PRBS or square-wave pattern (1111_0000).

Table 9 • 64b6xb Receive Data Path Blocks, PMA to Fabric Order

Rx Block Purpose

Rx Gearbox Locates block boundaries (configurable to 66-bit or 67-bit) in continuous stream of

32-bits data per clock beat from PMA. Removes the 2 or 3 bit headers and plays out the

64-bit data blocks in cyclic pattern of 32-bit clock beats with some inactive cycles.

Rx Disparity Inverts block based on header bit used in Interlaken.

Rx De-scrambler Implements IEEE 802.3 Clause 49 data de-scrambling. Same de-scrambling also

specified for use in Interlaken.

Rx 4B_to_8B Optionally widens the data path to 64-bits per clock beat.

Table 8 • 64b6xb Transmit Data Path Blocks, Fabric to PMA Order

Tx Block Purpose

TX

FWF

TX_{DATA,

HDR,

SOS,…}

8B to

4B

n*8+

Serializer

4*10

TXP, TXN

n is either 4 or 8, depending on configured serial speed

divide by 2

mux

n==8

n==4

div64

div32

TX_CLK

RX

FWF

RX_{DATA,

HDR,

SOS,…}

4B to

8B

n*8+

n*8+

De-Serializer

RXP, RXN

divide by 2

mux

n==8

n==4

div64 div32

RX_CLK

Clocks wires are colored per domain.

Data path is black. Blue labels are used

for system registers.

10

Scrambler

10

L64_R0/L64_CFG_BYPASS_8B_MODE

Disparity

10

PRBS Test

Gen

10

10

L64_R0/L64_CFG_BYPASS_SCRAMBLER

L64_R0/L64_CFG_BYPASS_DISPARITY

L64_R0/L64_CFG_BYPASS_GEARBOX

L64_R1/L64_BYPASS_TEST

10

Gearbox

Disparity

10

Gearbox

L64_R0/L64_CFG_GRBX_64B67B

Descrambler

10

10

PMA

PCS=64B6xB

FPGA

Fabric

Loading...

Loading...