Functional Description

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 59

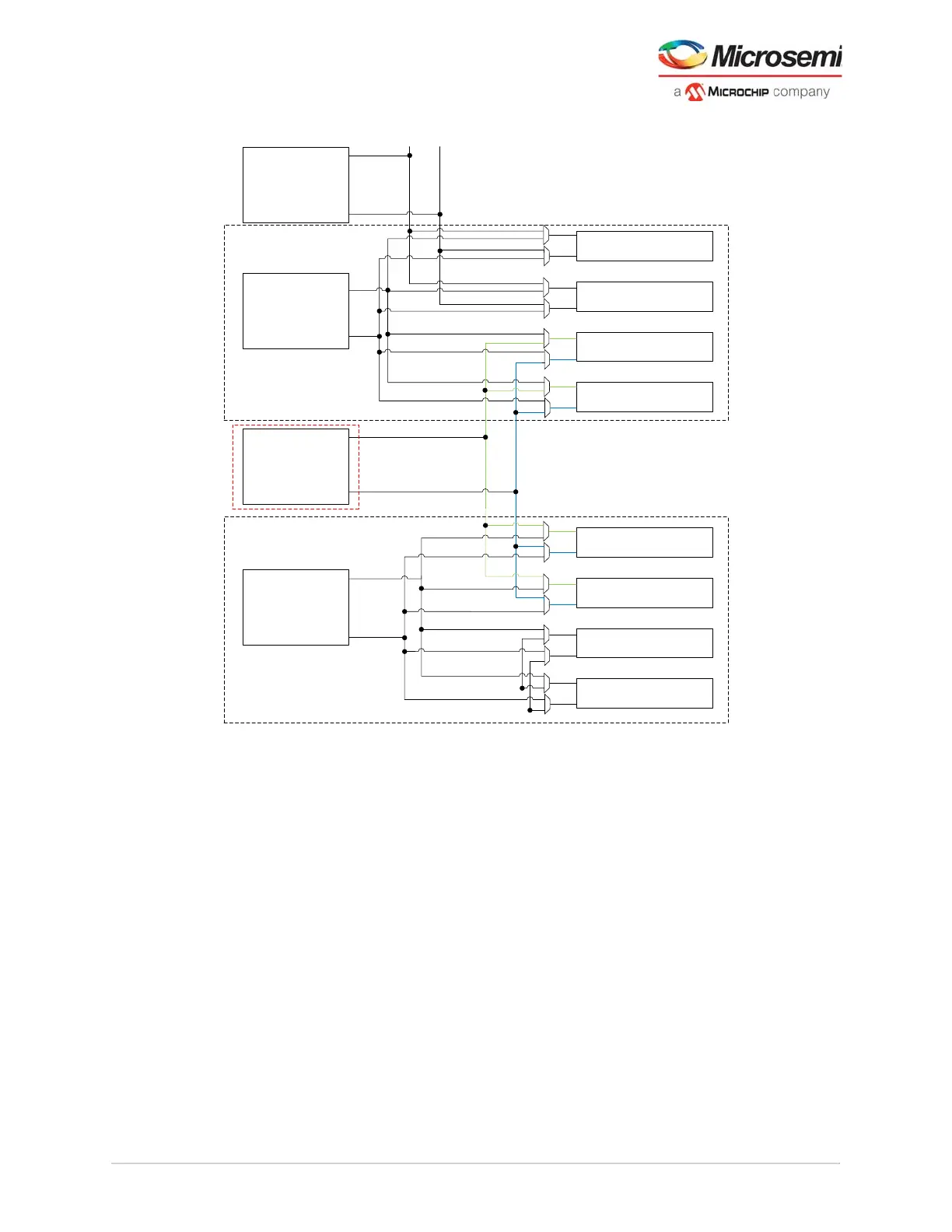

Figure 41 • Using TXPLLs For Upto Four Lanes

In the following scenarios, the quad based reset of TX lanes cannot be used:

• When one transmit clock is used for multiple lanes that do not belong to the same quad. In this

scenario, per lane reset of TX lanes must be used because the reset operation on one lane does not

affect the other lanes.

• When an arbitrary number of lanes more than four (5 to 8) need the transmit alignment.

TX_Bit_CLK

TX_Bit_CLK

TX_CLK_RESET

TXPLL1

TX_Bit_CLK

TX_CLK_RESET

TXPLL0

TX Lane

TX Lane

TX Lane

TX_Bit_CLK

TX_CLK_RESET

TXPLL_SSC

TX Lane

TX_CLK_RESET

TX_Bit_CLK

TX_CLK_RESET

TX_Bit_CLK

TX_CLK_RESET

TX_Bit_CLK

TX_CLK_RESET

TX_Bit_CLK

QUAD

TX Lane

TX Lane

TX Lane

TX_Bit_CLK

TX_CLK_RESET

TXPLL_SSC

TX Lane

TX_CLK_RESET

TX_Bit_CLK

TX_CLK_RESET

TX_CLK_RESET

TX_Bit_CLK

TX_CLK_RESET

TX_Bit_CLK

QUAD

Loading...

Loading...