Implementation

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 90

For more information about jitter cleaning operation, see Jitter Attenuator, page 63.

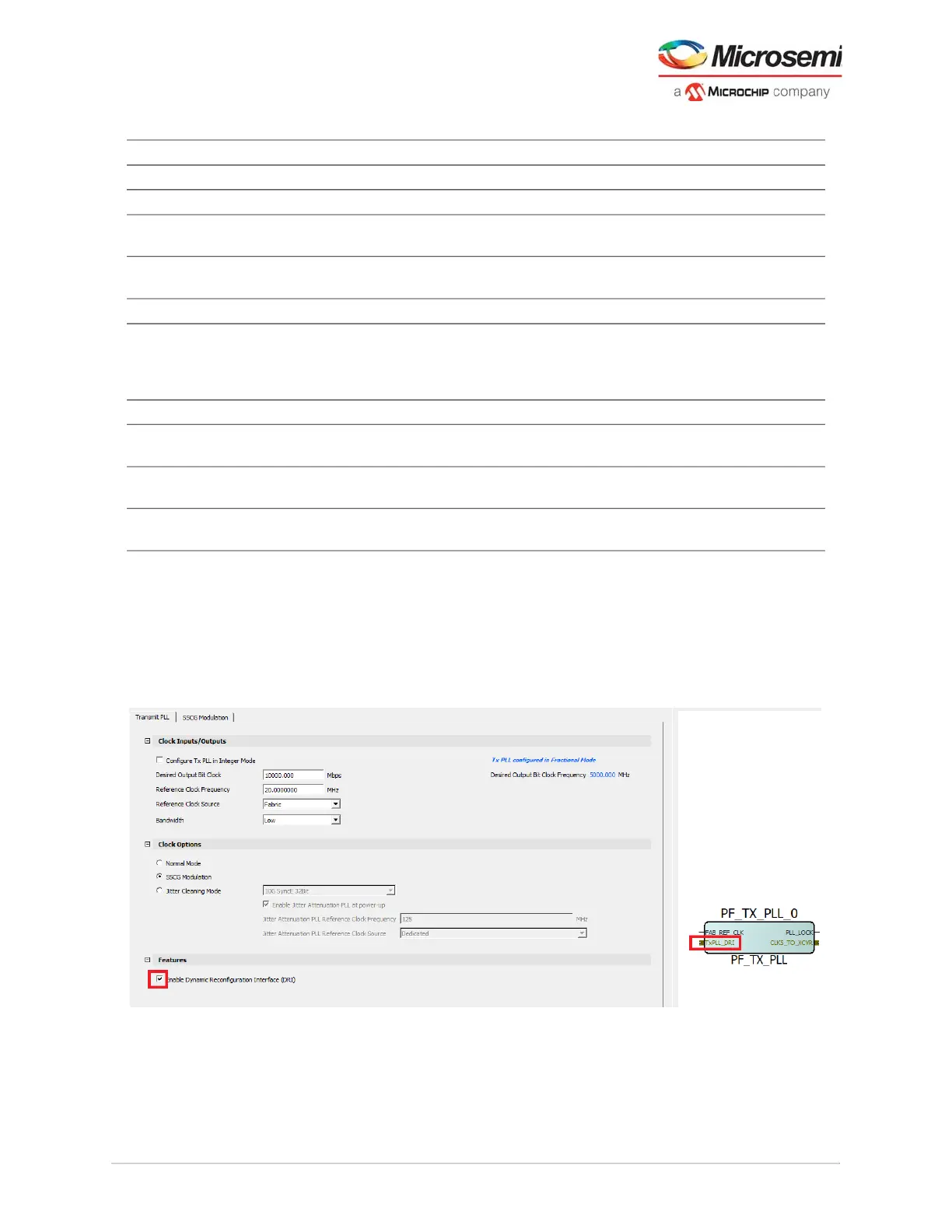

8. Click Enable Dynamic Reconfiguration Interface (DRI) checkbox to add the ports needed to

connect the Transmit PLL to the DRI. See UG0725: PolarFire FPGA Device Power-Up and Resets

User Guide for more information on DRI usage and specifications.

Figure 70 • Enable Dynamic reconfiguration Interface

9. Click OK after making desired selections.

Table 28 • Spread Spectrum

Options Default Details

Modulation Frequency

Target User entry 64 KHz Target Spread Spectrum modulation.

Calculated 60.0962 KHz Calculation is based on TXPLL

reference clock settings.

Spread Mode Down spread/Center

Spread

Down Configures the modulation style

Spread/Divval

Spread Pull down 0 Sets up to 32 divider settings

(0, 01.,....3.1). This value sets the

percent of modulation amplitude down

or center spread.

Wave Table

Internal (128) Enabled Selects internal 128 point triangle

wave

Pseudo-random Noise

Modulation Source

Disabled Selection between 3 predefined

modulation patterns.

Enable Random Noise Filter Enable/Disable

1

Disabled Enable to turn on filtering to reduce

jitter if needed.

1. When pseudo-random noise modulation source is enabled after the user selects one of the predefined modulation patterns.

The optional high pass filtered PRBS is modulated to the PLL reducing the harmonic frequency amplitude peaks.

Loading...

Loading...