Implementation

Microsemi Proprietary and Confidential UG0677 User Guide Revision 9.0 89

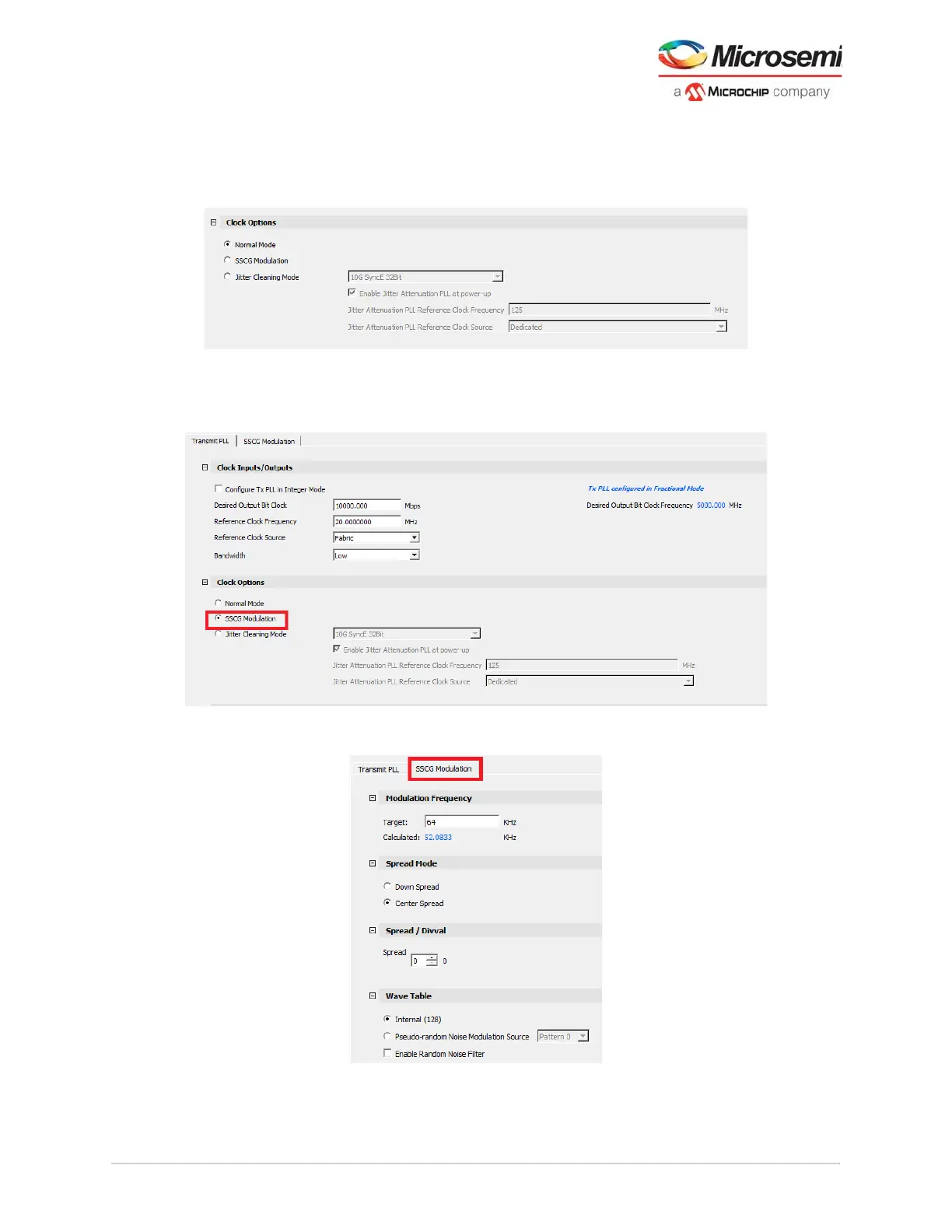

Normal Mode configures the TX PLL to default operation based on the clock Inputs/Outputs setting.

Whereas, Jitter Cleaning mode customizes the attenuation coefficients for the pre-defined standards to

be used where the recovered clock can be used as a TX reference clock to meet protocol jitter

specifications.

Figure 67 • Clock Options

5. Click Spread Spectrum clock generation mode (Not available prior to Libero SoC v12.3). This

feature allows spread-spectrum generation to be enable from the transmit phase-locked loop. See

DS0141: PolarFire FPGA Datasheet for more information on spread spectrum specifications.

Figure 68 • Spread Spectrum Clock Generation Enable

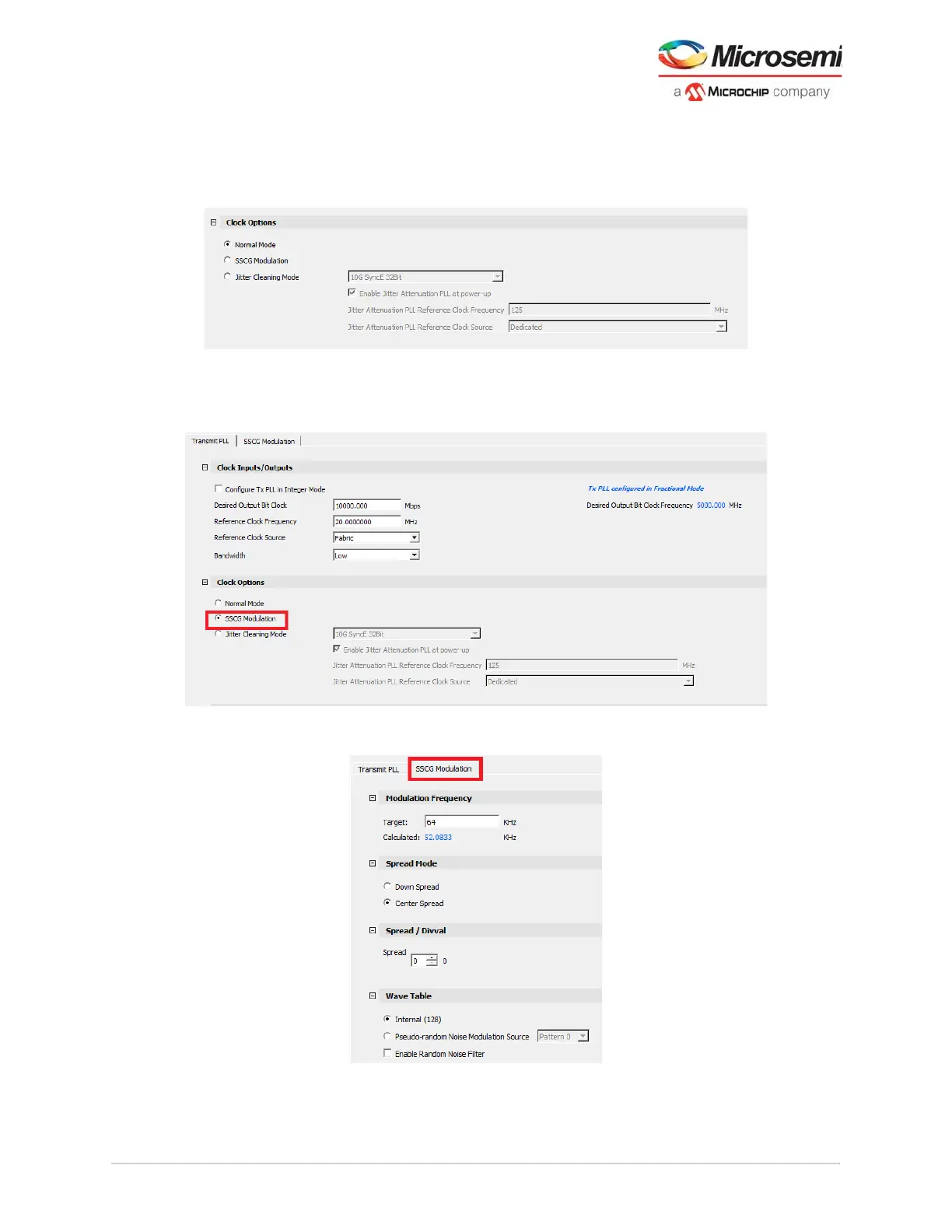

6. Select SSCG mode to enable the SSCG Modulation Feature tab.

Figure 69 • Spread Spectrum Modulation Options

7. Click OK after making desired selections.

For more information about Spread Spectrum, see Spread Spectrum Clocking, page 57.

Loading...

Loading...