Memory Interface

3-8 Copyright © 2001, 2004 ARM Limited. All rights reserved. ARM DDI 0210C

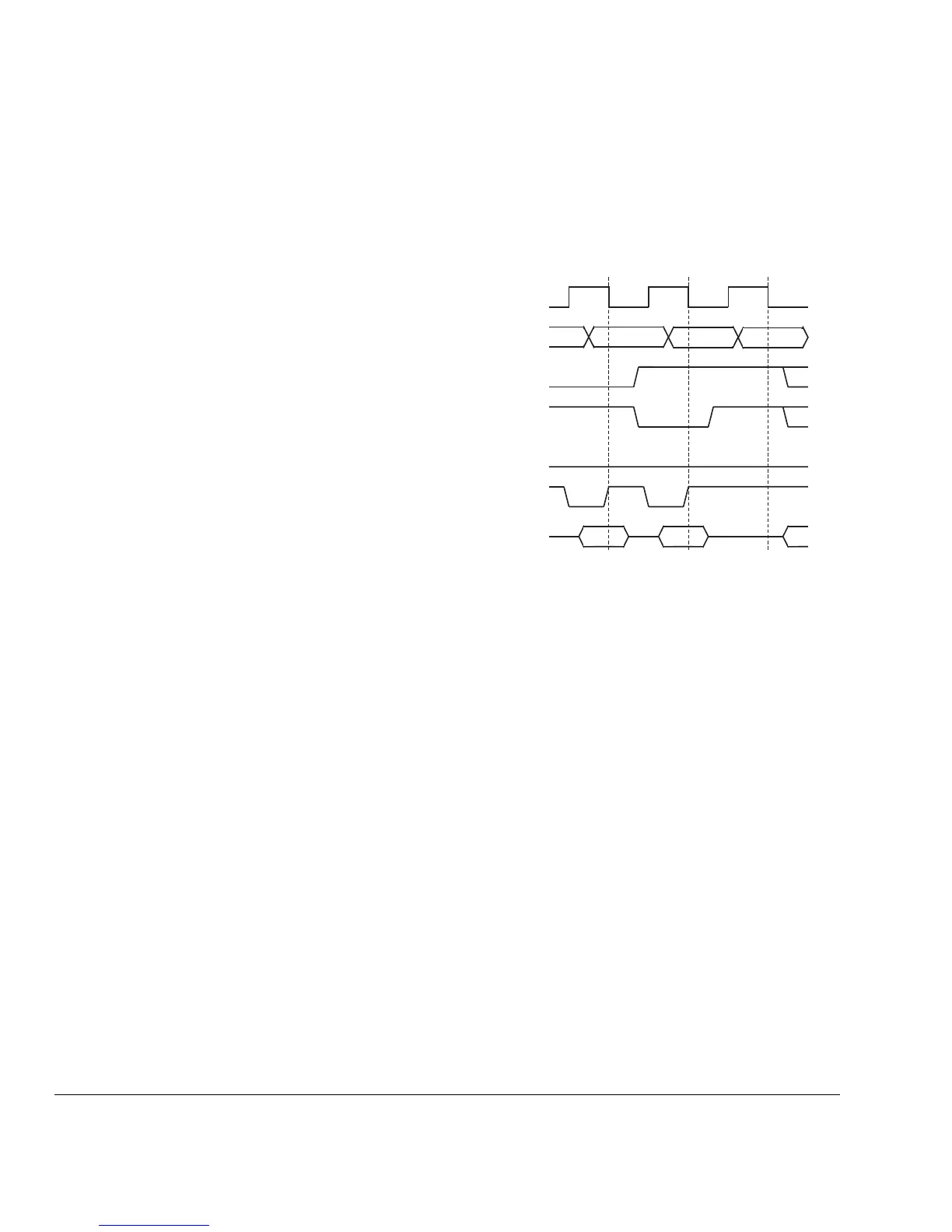

Where possible the ARM7TDMI processor broadcasts the address for the next access,

so that decode can start, but the memory controller must not commit to a memory

access. This is shown in Figure 3-4 and, is further described in Nonsequential memory

cycle on page 3-6.

Figure 3-4 Internal cycles

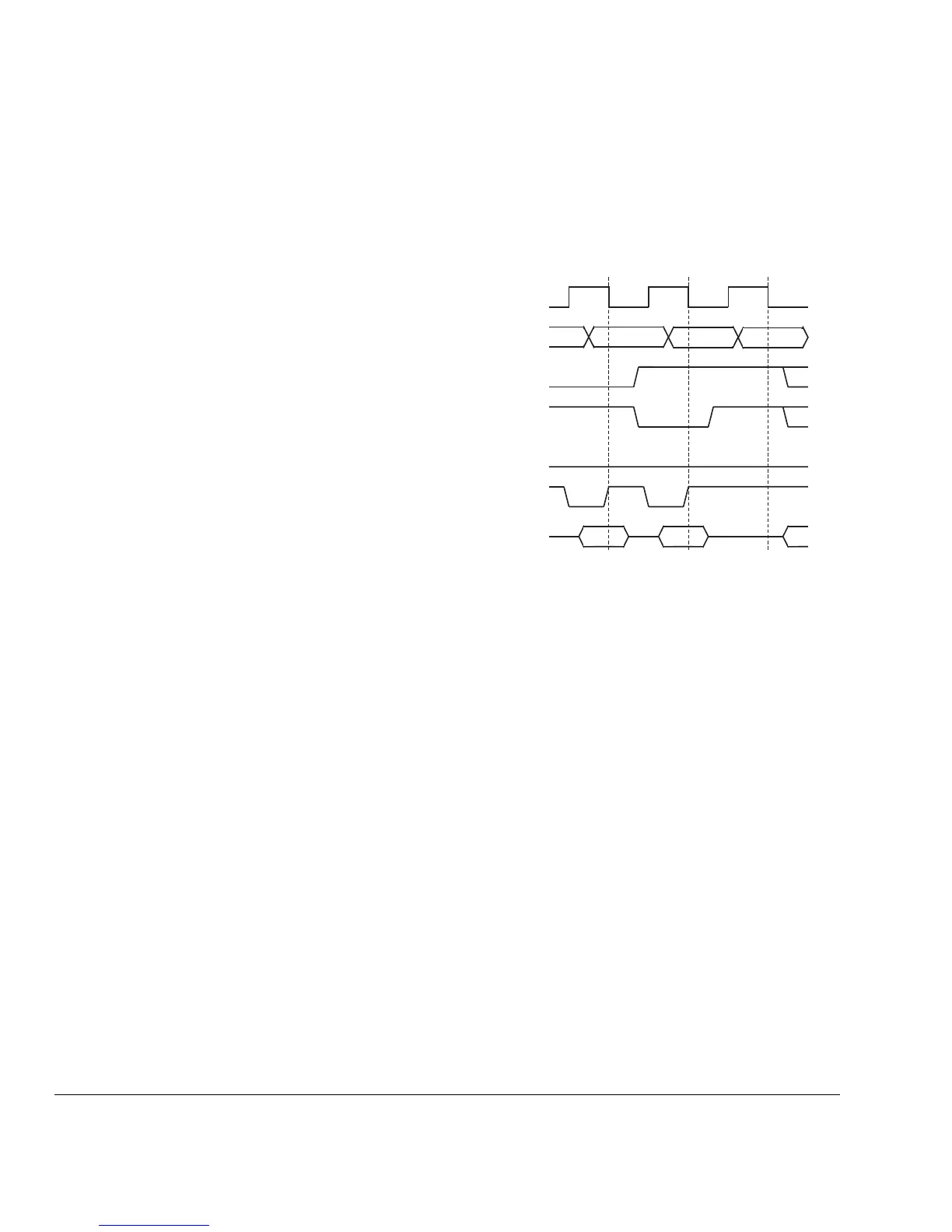

3.3.4 Merged IS cycles

Where possible, the ARM7TDMI processor performs an optimization on the bus to

allow extra time for memory decode. When this happens, the address of the next

memory cycle is broadcast on this bus during an internal cycle. This enables the

memory controller to decode the address, but it must not initiate a memory access

during this cycle. In a merged IS cycle, the next cycle is a sequential cycle to the same

memory location. This commits to the access, and the memory controller must initiate

the memory access. This is shown in Figure 3-5 on page 3-9.

N-cycle S-cycle

a+4 a+8

I-cycle C-cycle

a

a+12

MCLK

A[31:0]

nMREQ

SEQ

nRAS

nCAS

D[31:0]

Loading...

Loading...