5-96 F650 Digital Bay Controller GE Multilin

5.5 CONTROL ELEMENTS 5 SETPOINTS

5

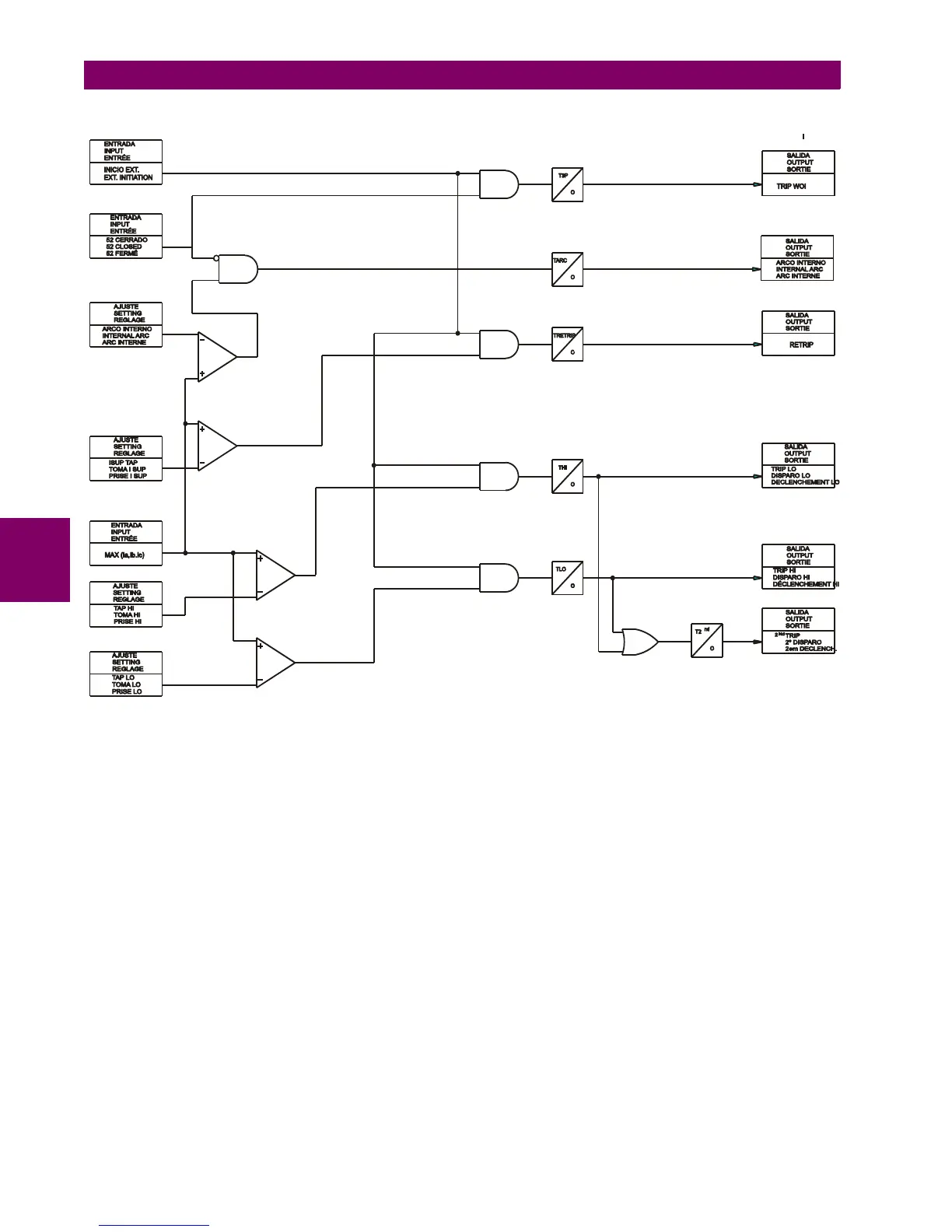

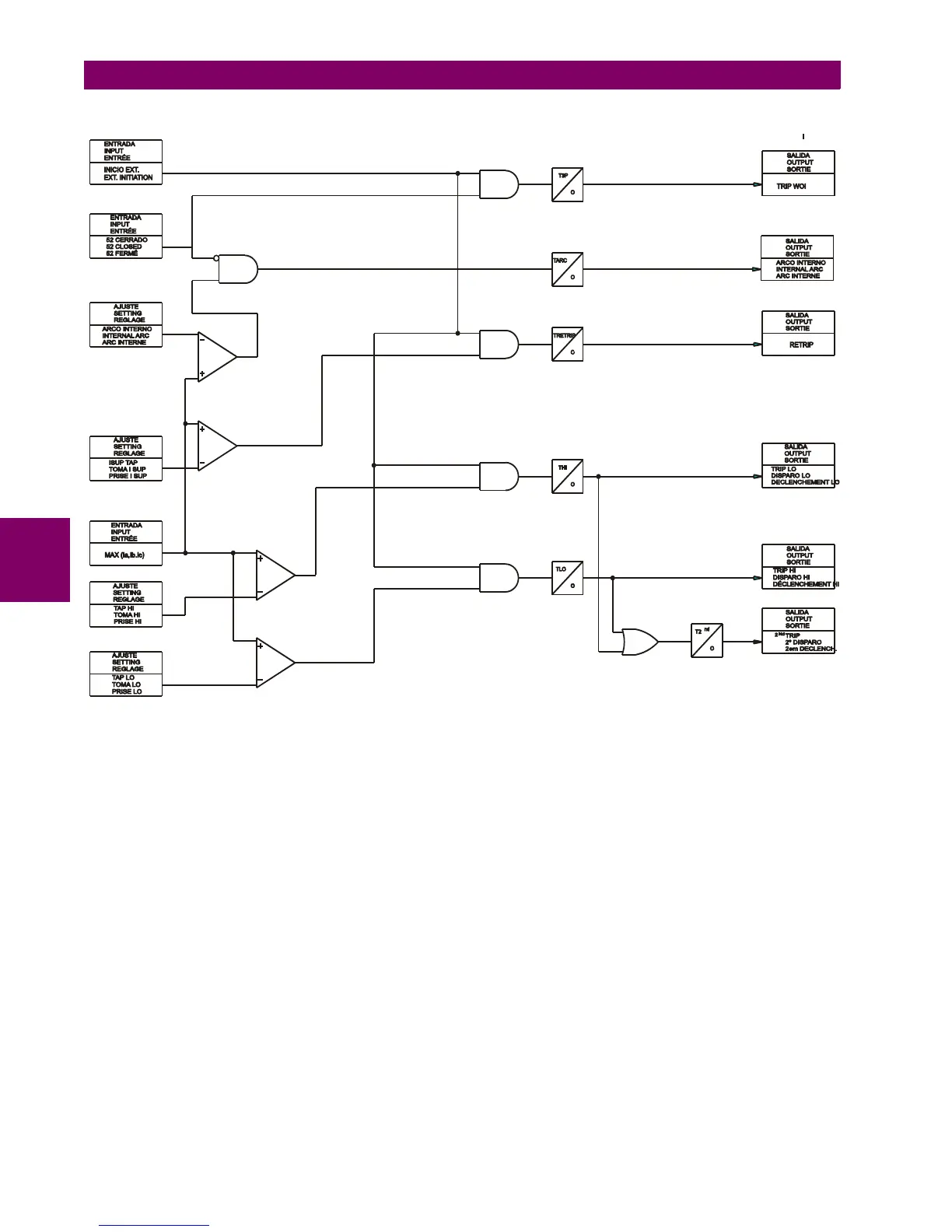

The following figure shows the logic scheme for the breaker failure unit:

Figure 5–26: LOGIC SCHEME FOR 50BF

The breaker failure unit has three levels. The first one is called “Retrip” or “Supervision”. This operation level can be used to

give a signal to the breaker on which the initial opening has been executed. This is sometimes a usual practice; 50

milliseconds after the trip signal, a retrip signal is sent to the breaker.

Besides the supervision or retrip level, there are two additional levels, known as “Hiset” and “Lowset”. These two levels,

together with their time delays, allow executing complex protection schemes. Additionally to these two supervision levels,

there is a second time stage called “second step”.

Operation of breaker failure units by level (supervision, hiset and loset) is produced when the current level is higher than

the set current for the pickup of each level during the time set in the corresponding delay setpoint.

High and low levels constitute a second step level; for the pickup of this second level, only the pickup of any of the two

levels (hiset and loset) is required. For the unit pickup to dropout it is required that the current is under the pickup levels of

both hiset and loset setpoints. Once the second level time delay has expired, a “Second Step” trip signal will be issued.

50BF unit incorporates also a no current tripping unit, and an internal arc unit. The no-current rip unit is governed only by

the status of the breaker auxiliary contact; once the external breaker failure initiation signal is received, if the breaker status

does not change to open during the set time in the unit (No Current Delay), the corresponding breaker failure signal is

issued (BKR FAIL NO CURRENT),

The internal arc unit inside the breaker failure element is independent from the external breaker failure signal; this unit is

used to detect arcing produced with an open breaker; if a higher current that the set level is detected during a period that is

longer than the set delay for the unit (Internal Arc Delay), and the breaker is open, the corresponding internal arc signal will

be issued (INTERNAL ARC).

Loading...

Loading...