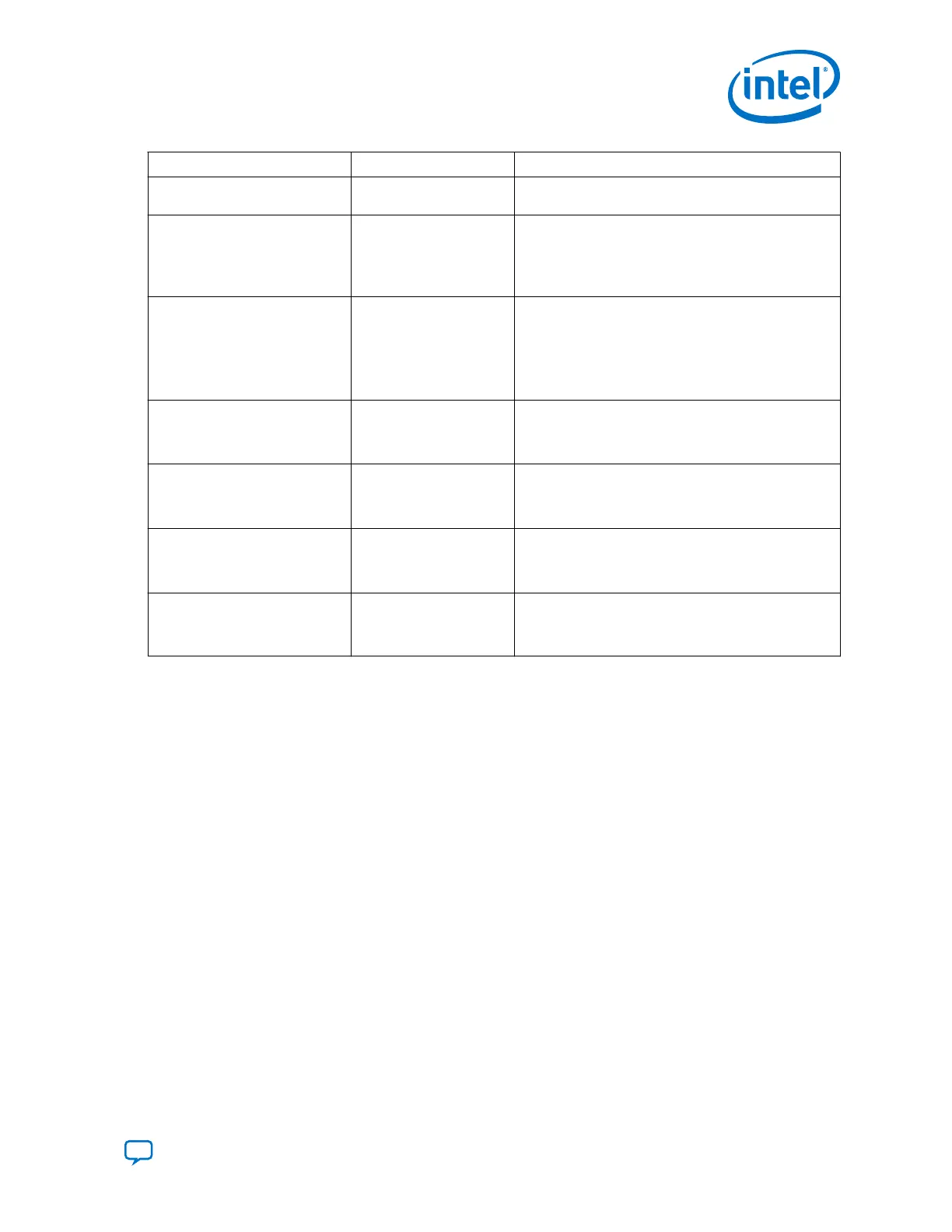

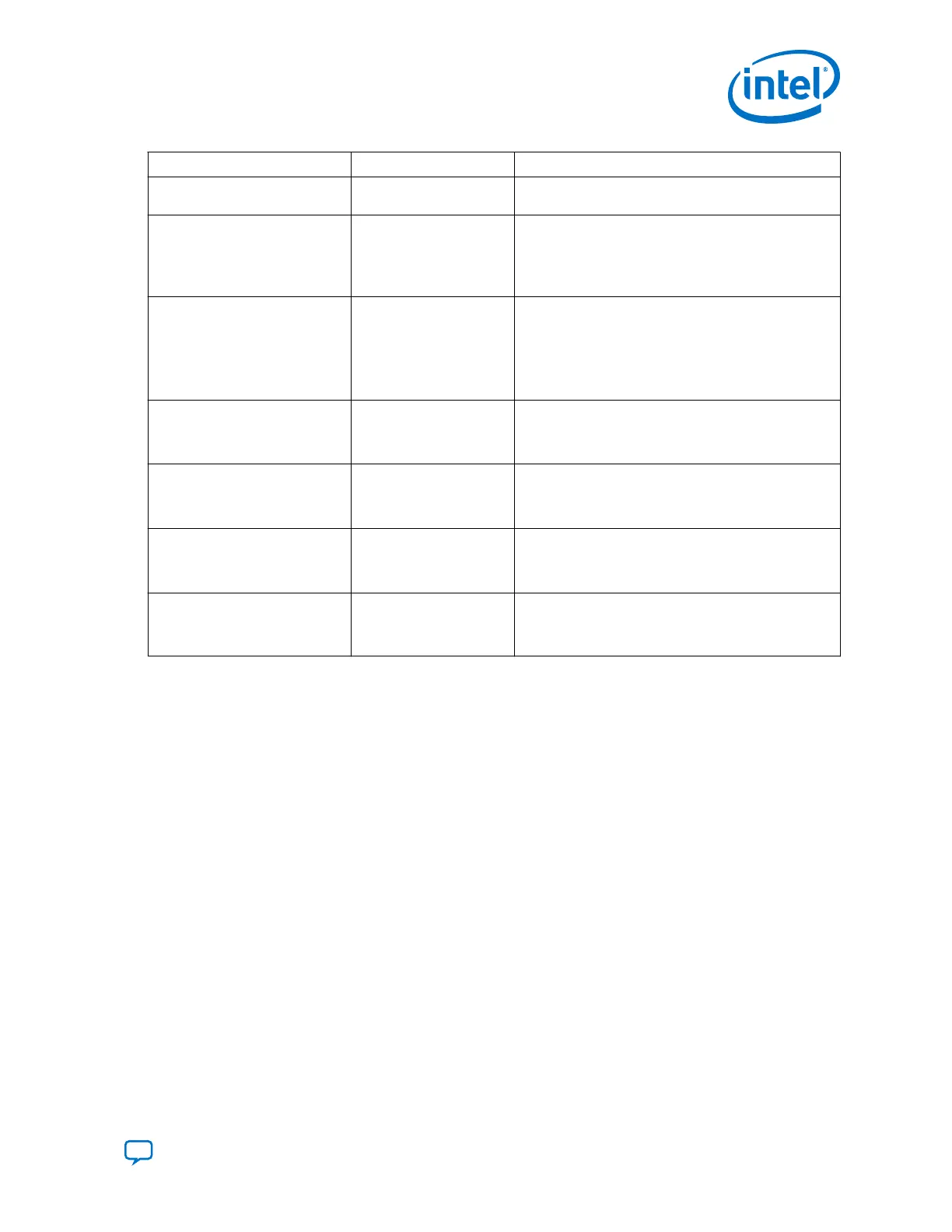

Name Value Description

Note: This option is not available for Intel Cyclone 10

GX devices.

Selected TX PMA local clock

division factor for 2.5 GbE

1, 2

This parameter is the local clock division factor in the

2.5G mode. It is directly mapped to the Native PHY IP

Core GUI options.

Note: This option is not available for Intel Cyclone 10

GX devices.

Enable Altera Debug Master

Endpoint

On, Off Available in Native PHY and TX PLL IP parameter editors.

When enabled, the Altera Debug Master Endpoint

(ADME) is instantiated and has access to the Avalon-MM

interface of the Native PHY. You can access certain test

and debug functions using System Console with the

ADME. Refer to the Embedded Debug Features section

for more details about ADME.

Enable capability registers On, Off Available in Native PHY and TX PLL IP parameter editors.

Enables capability registers. These registers provide

high-level information about the transceiver channel's/

PLL's configuration.

Set user-defined IP identifier User-specified Available in Native PHY and TX PLL IP parameter editors.

Sets a user-defined numeric identifier that can be read

from the user_identifier offset when the capability

registers are enabled.

Enable control and status

registers

On, Off Available in Native PHY and TX PLL IP parameter editors.

Enables soft registers for reading status signals and

writing control signals on the PHY/PLL interface through

the ADME or reconfiguration interface.

Enable PRBS soft

accumulators

On, Off Available in Native PHY IP parameter editor only.

Enables soft logic to perform PRBS bit and error

accumulation when using the hard PRBS generator and

checker.

Related Information

Embedded Debug Features on page 353

2.6.3.3. Functional Description

The 1G/2.5G/5G/10G Multi-rate PHY Intel FPGA IP core for Intel Cyclone 10 GX

devices implements the 10M to 10Gbps Ethernet PHY in accordance with the IEEE

802.3 Ethernet Standard. This IP core handles the frame encapsulation and flow of

data between a client logic and Ethernet network via a 10M to 10GbE PCS and PMA

(PHY).

2. Implementing Protocols in Intel Cyclone 10 GX Transceivers

UG-20070 | 2018.09.24

Send Feedback

Intel

®

Cyclone

®

10 GX Transceiver PHY User Guide

111

Loading...

Loading...