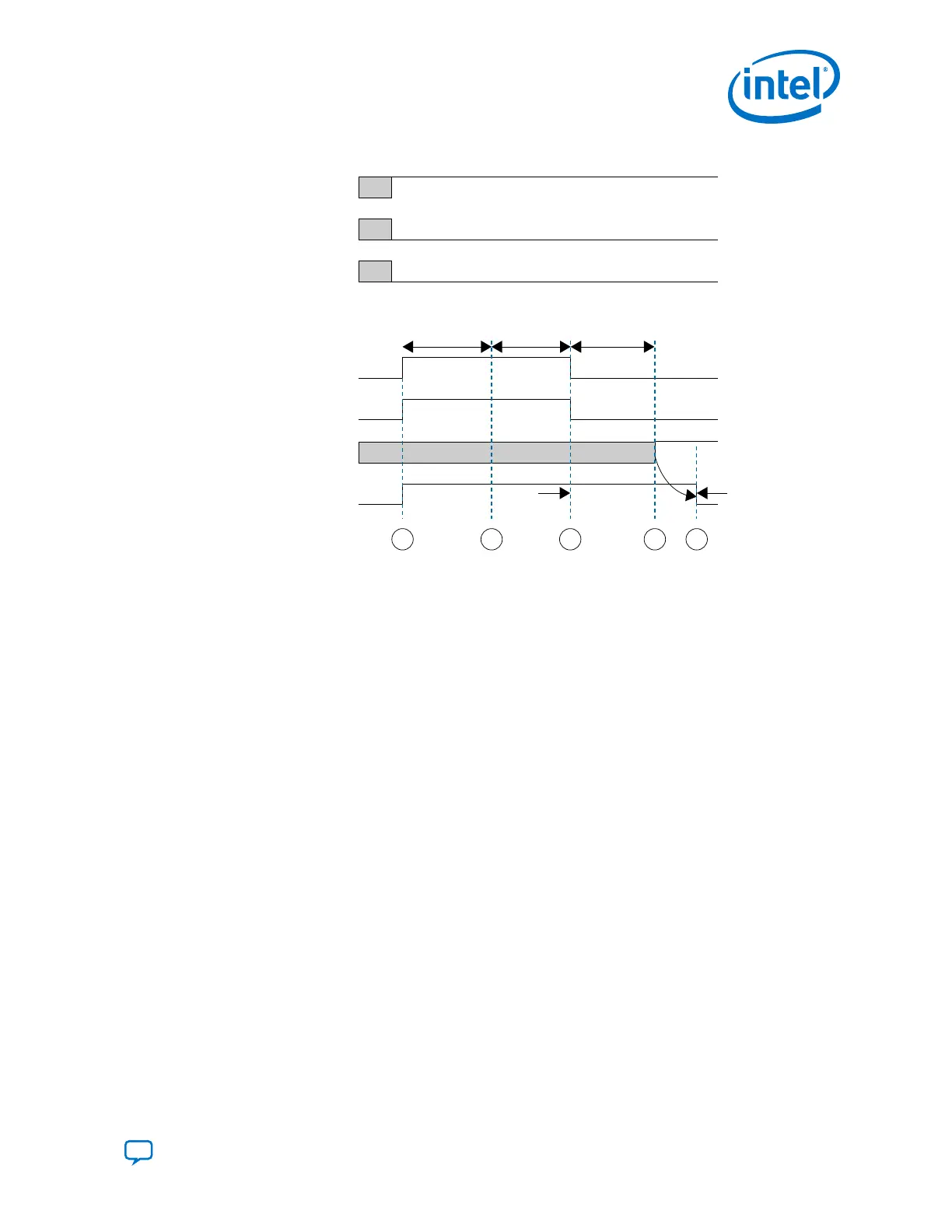

Figure 153. Dynamic Reconfiguration of Transmitter Channel During Device Operation

Device Power Up

pll_cal_busy

tx_cal_busy

tx_analogreset

pll_powerdown

pll_locked

tx_digitalreset

1 3

5

2

Legal

Reconfiguration

Window

4

t

req

t

req

t

tx_digitalreset

(1)

t

req

= 70 μs

Note:

(1) The Cyclone 10 GX Default setting presets ttx_digitalreset to 70 μs.

(2) Area in gray is don’t care zone.

RX Channel

The numbers in this list correspond to the numbers in the following figure.

1.

Assert rx_analogreset and rx_digitalreset. Ensure that rx_cal_busy is

low. You must reset the PCS by asserting rx_digitalreset every time you

assert rx_analogreset.

2. Perform dynamic reconfiguration after minimum 70 μs of asserting

rx_analogreset.

3.

Deassert rx_analogreset after performing dynamic reconfiguration.

4.

The rx_is_lockedtodata signal goes high after the CDR acquires lock.

5.

Ensure rx_is_lockedtodata is asserted for t

LTD

(minimum of 4 μs) before

deasserting rx_digitalreset.

4. Resetting Transceiver Channels

UG-20070 | 2018.09.24

Send Feedback

Intel

®

Cyclone

®

10 GX Transceiver PHY User Guide

253

Loading...

Loading...