RL78/G1H CHAPTER 18 RF TRANSCEIVER

R01UH0575EJ0120 Rev. 1.20 Page 588 of 920

Dec 22, 2016

(22) Timer compare registers 0 and 1

(BBTCOMP0REG0 to BBTCOMP2REG0, BBTCOMP0REG1 to BBTCOMP2REG1)

These registers are used to compare with the 32-bit timer. Each of them includes three channels to compare

each of the channels with the 32-bit timer.

The BBTCOMP0REG0 to BBTCOMP2REG0 and BBTCOMP0REG1 to BBTCOMP2REG1 registers consist

of 16 bits and can be accessed (serial interface communication) in 8 bit unit.

Reset signal generation clears these registers to 0000H.

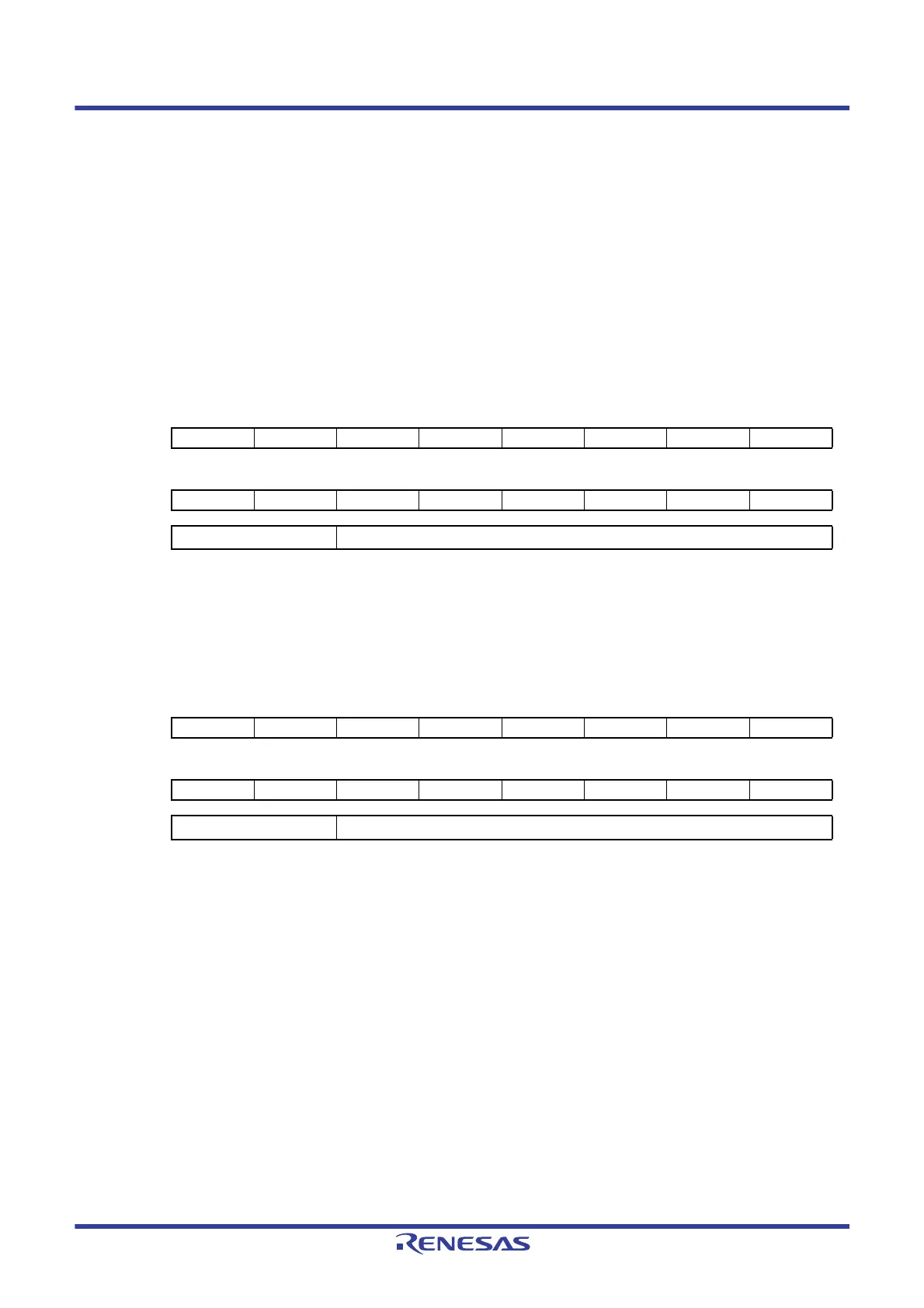

Figure 18 - 29 Timer Compare Register 0 (BBTCOMP0REG0 to BBTCOMP2REG0) Format

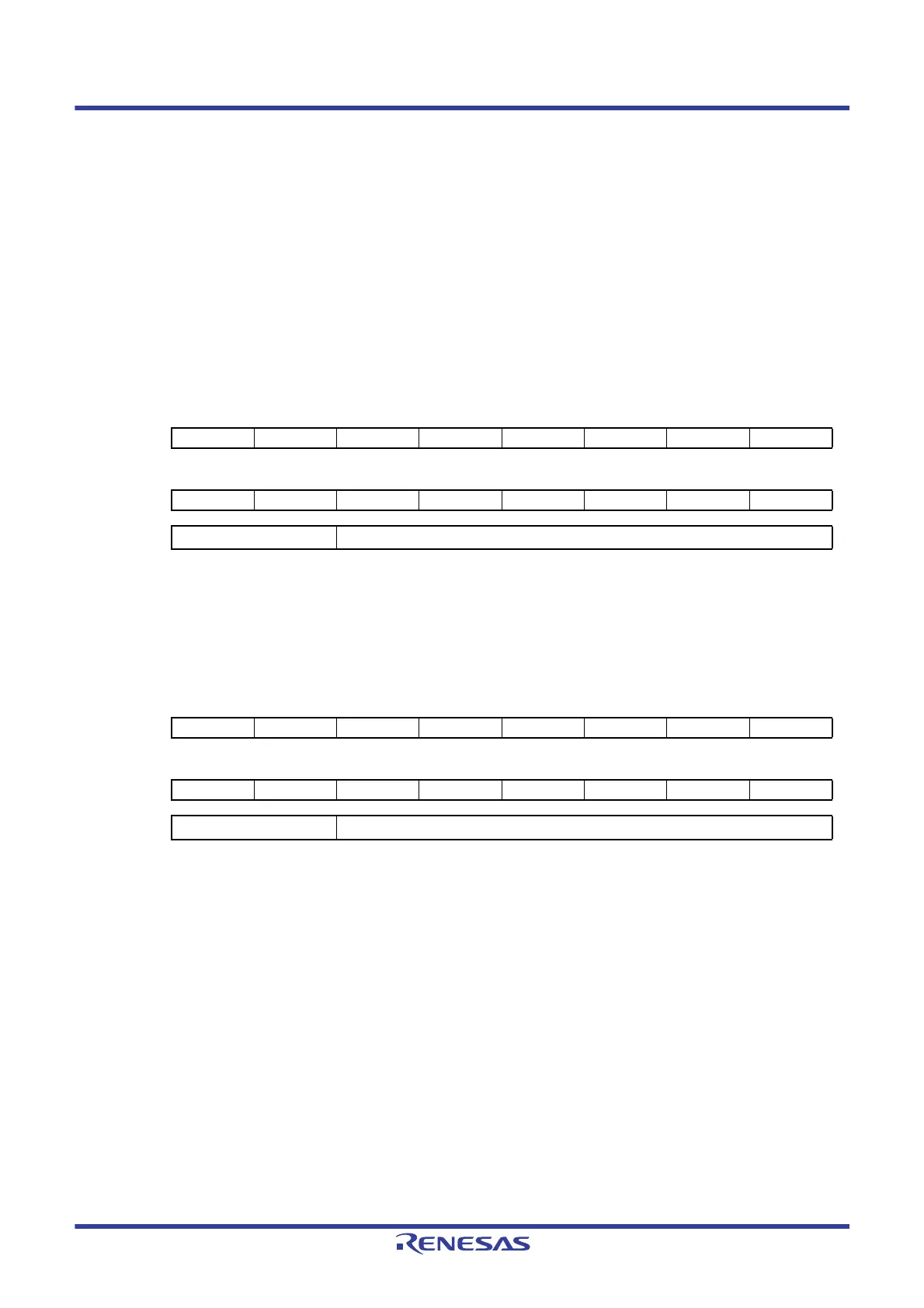

Figure 18 - 30 Timer Compare Register 1 (BBTCOMP0REG1 to BBTCOMP2REG1) Format

Address:

002DH, 002CH (BBTCOMP2REG0), 0029H, 0028H (BBTCOMP1REG0), 0025H, 0024H (BBTCOMP0REG0)

After reset:

0000H

R/W

Symbol 15 14 13 12 11 10 9 8

BBTCOMP

nREG0

(n = 0 to 2)

76543210

BBTCOMPnREG0 Lower bits of the 32-bit compare (bits 15 to 0) (n = 0 to 2)

Address:

002FH, 002EH (BBTCOMP2REG1), 002BH, 002AH (BBTCOMP1REG1), 0027H, 0026H (BBTCOMP0REG1)

After reset:

0000H

R/W

Symbol 15 14 13 12 11 10 9 8

BBTCOMP

nREG1

(n = 0 to 2)

76543210

BBTCOMPnREG1 Upper bits of the 32-bit compare (bits 31 to 16) (n = 0 to 2)

Loading...

Loading...