RL78/G1H CHAPTER 14 SERIAL ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 350 of 920

Dec 22, 2016

14.3.14 Noise filter enable register 0 (NFEN0)

The NFEN0 register is used to set whether the noise filter can be used for the input signal from the serial data

input pin to each channel.

Disable the noise filter of the pin used for CSI communication, by clearing the corresponding bit of this register to

0.

Enable the noise filter of the pin used for UART communication, by setting the corresponding bit of this register to

1.

When the noise filter is enabled, after synchronization is performed with the operation clock (f

MCK) of the target

channel, 2-clock match detection is performed. When the noise filter is OFF, only synchronization is performed

with the Operation clock of target channel (f

MCK).

The NFEN0 register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears the NFEN0 register to 00H.

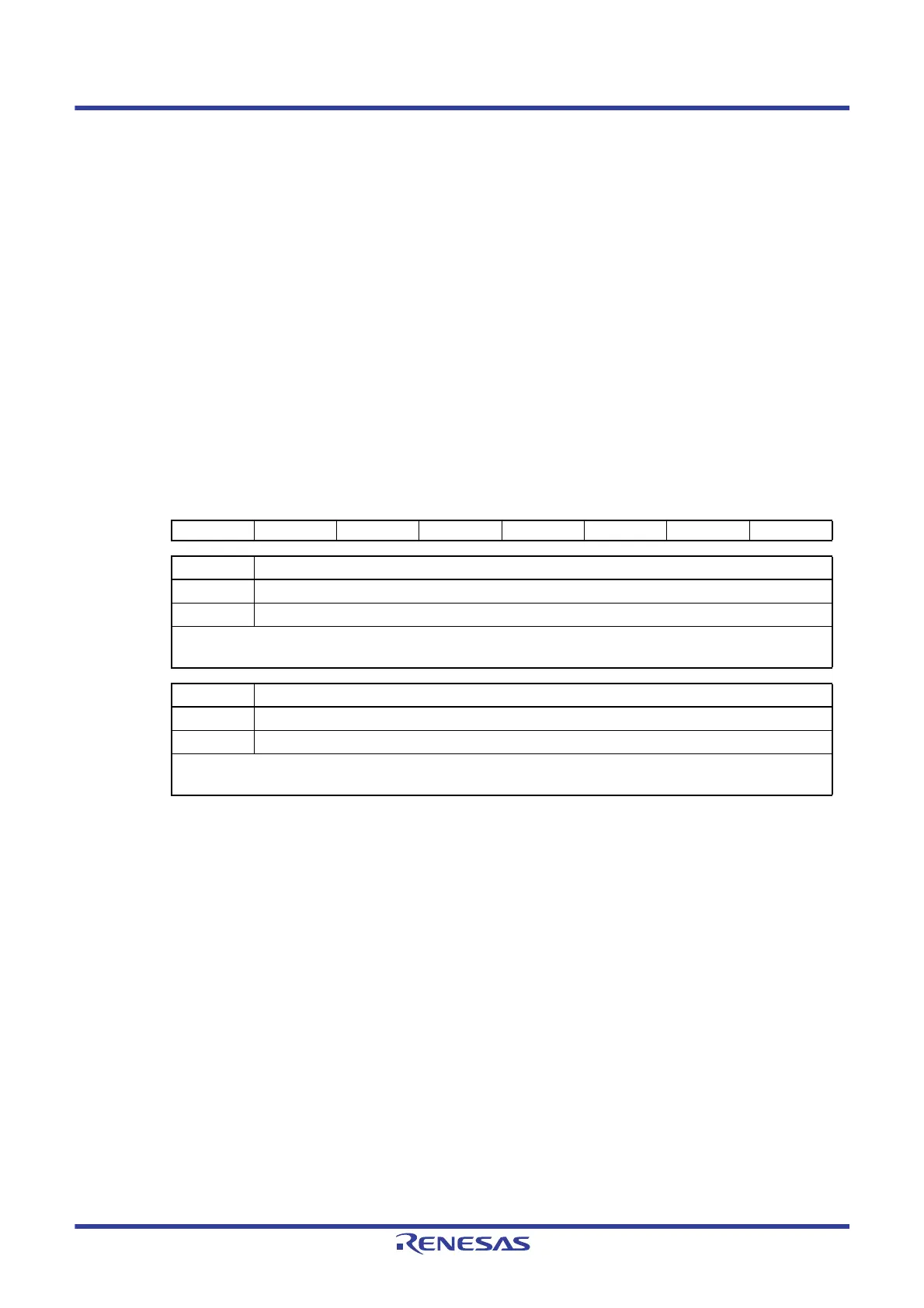

Figure 14 - 21 Format of Noise filter enable register 0 (NFEN0)

Address: F0070H After reset: 00H R/W

Symbol76543210

NFEN0 0 SNFEN30 0 0 0 SNFEN10 0 0

SNFEN30 Use of noise filter of RxD3 pin

0 Noise filter OFF

1 Noise filter ON

Set SNFEN30 to 1 to use the RxD3 pin.

Clear SNFEN30 to 0 to use the other than RxD3 pin.

SNFEN10 Use of noise filter of RxD1 pin

0 Noise filter OFF

1 Noise filter ON

Set the SNFEN10 bit to 1 to use the RxD1 pin.

Clear the SNFEN10 bit to 0 to use the other than RxD1 pin.

Loading...

Loading...