RL78/G1H CHAPTER 8 TIMER RJ

R01UH0575EJ0120 Rev. 1.20 Page 225 of 920

Dec 22, 2016

8.3 Registers Controlling Timer RJ

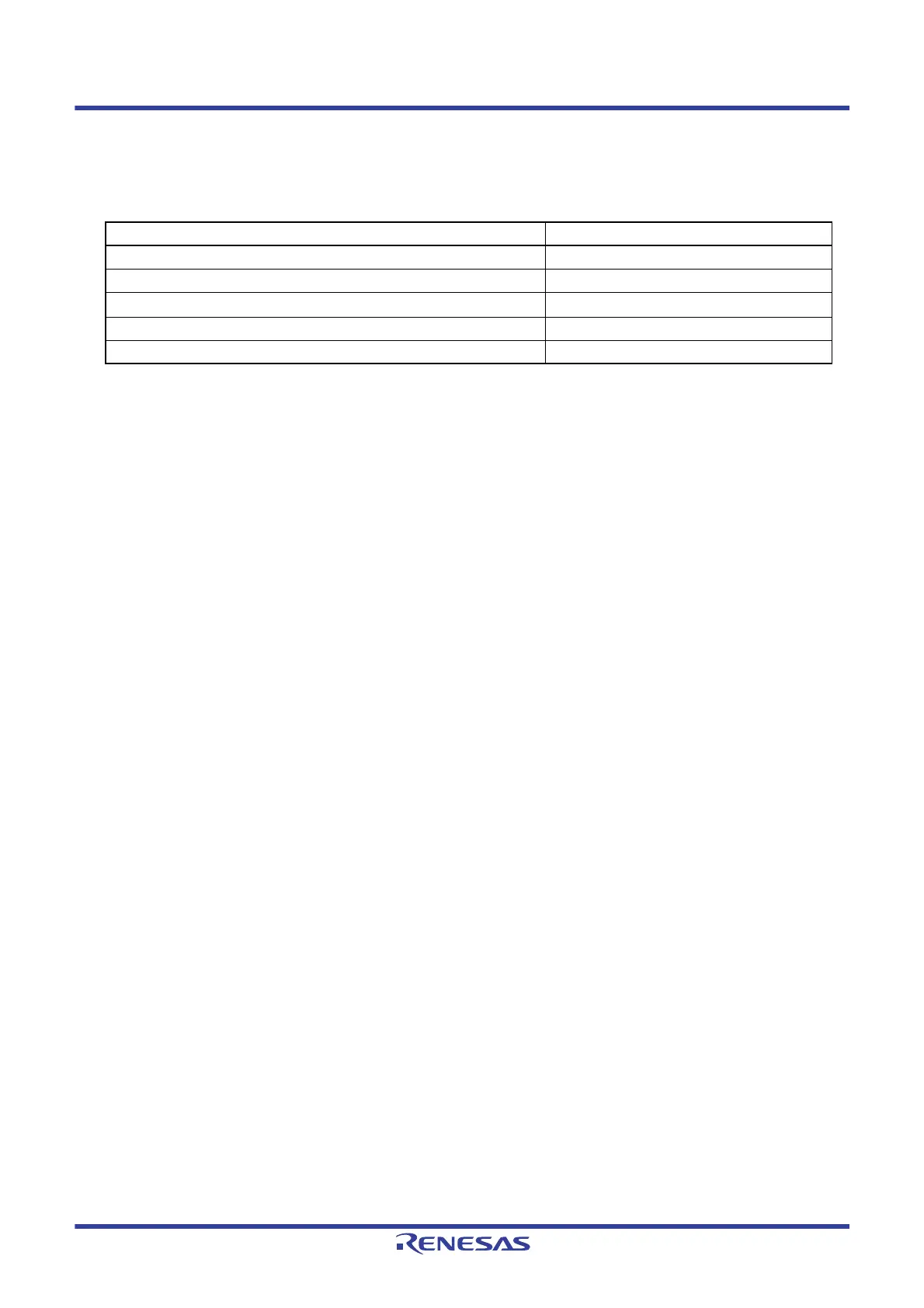

Table 8 - 2 lists the Registers Controlling Timer RJ.

Note When the TRJ0 register is accessed, the CPU does not proceed to the next instruction processing but enters the wait state

for CPU processing. For this reason, if this wait state occurs, the number of instruction execution clocks is increased by the

number of wait clocks. The number of wait clocks for access to the TRJ0 register is one clock for both writing and reading.

Table 8 - 2 Registers Controlling Timer RJ

Register Name Symbol

Peripheral enable register 1 PER1

Subsystem clock supply mode control register OSMC

Timer RJ counter register 0

Note

TRJ0

Timer RJ control register 0 TRJCR0

Timer RJ mode register 0 TRJMR0

Loading...

Loading...