RL78/G1H CHAPTER 23 VOLTAGE DETECTOR

R01UH0575EJ0120 Rev. 1.20 Page 762 of 920

Dec 22, 2016

23.3.1 Voltage detection register (LVIM)

This register is used to specify whether to enable or disable rewriting the voltage detection level register (LVIS),

as well as to check the LVD output mask status.

This register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

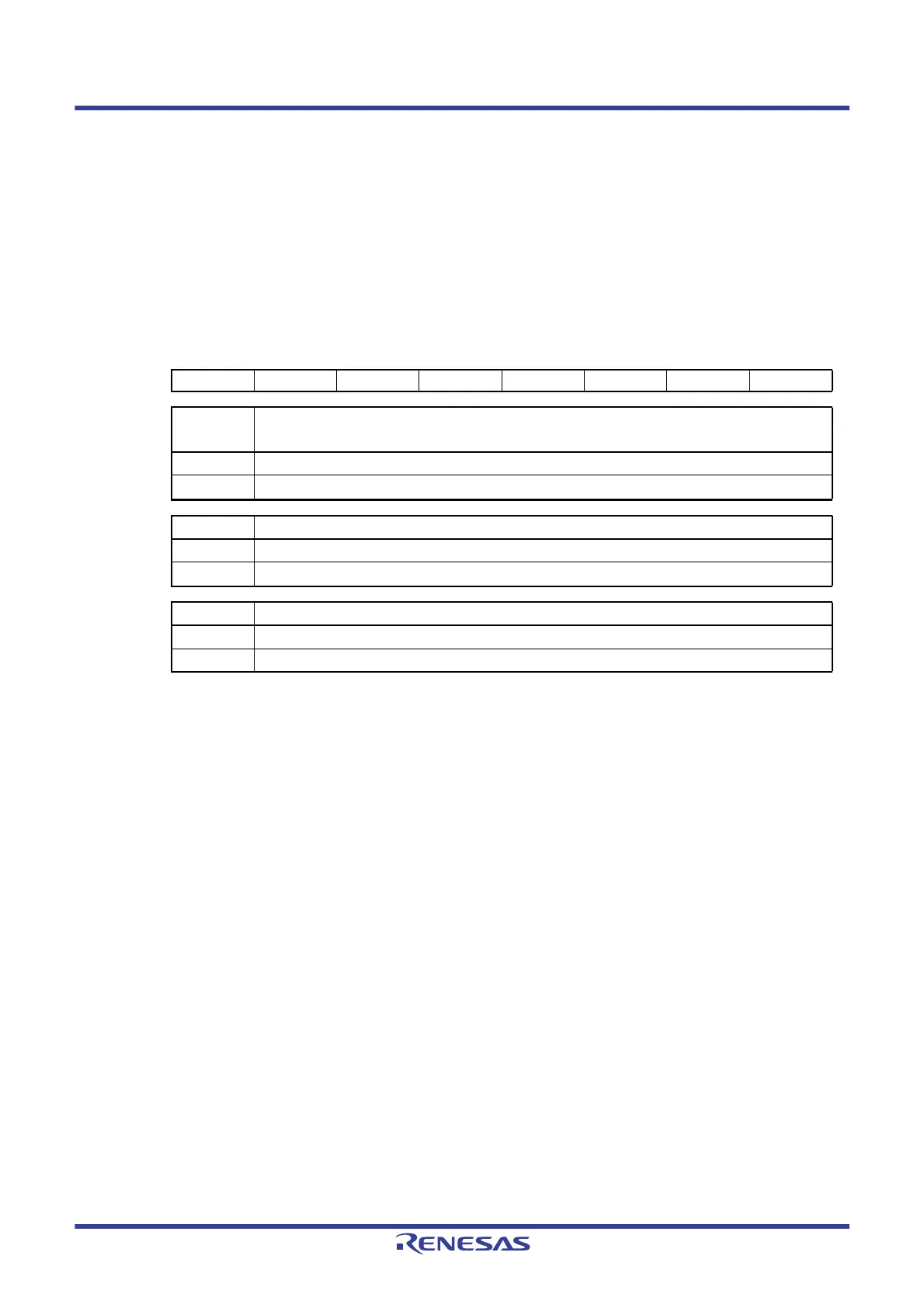

Figure 23 - 2 Format of Voltage detection register (LVIM)

Note 1. The reset value changes depending on the reset source.

If the LVIM register is reset by LVD, it is not reset but holds the current value. In other reset, LVISEN is

cleared to 0.

Note 2. Bits 0 and 1 are read-only.

Note 3. LVISEN can only be set in the interrupt & reset mode (option byte LVIMDS1, LVIMDS0 = 1, 0). Do not change

the initial value in other modes.

Note 4. LVIOMSK bit is only automatically set to “1” when the interrupt & reset mode is selected (option byte

LVIMDS1, LVIMDS0 = 1, 0) and reset or interrupt by LVD is masked.

• Period during LVISEN = 1

• Waiting period from the time when LVD interrupt is generated until LVD detection voltage becomes stable

• Waiting period from the time when the value of LVILV bit changes until LVD detection voltage becomes

stable

Address: FFFA9H After reset: 00H

Note 1

R/W

Note 2

Symbol<7>65432<1><0>

LVIM

LVISEN

Note 3

00000LVIOMSKLVIF

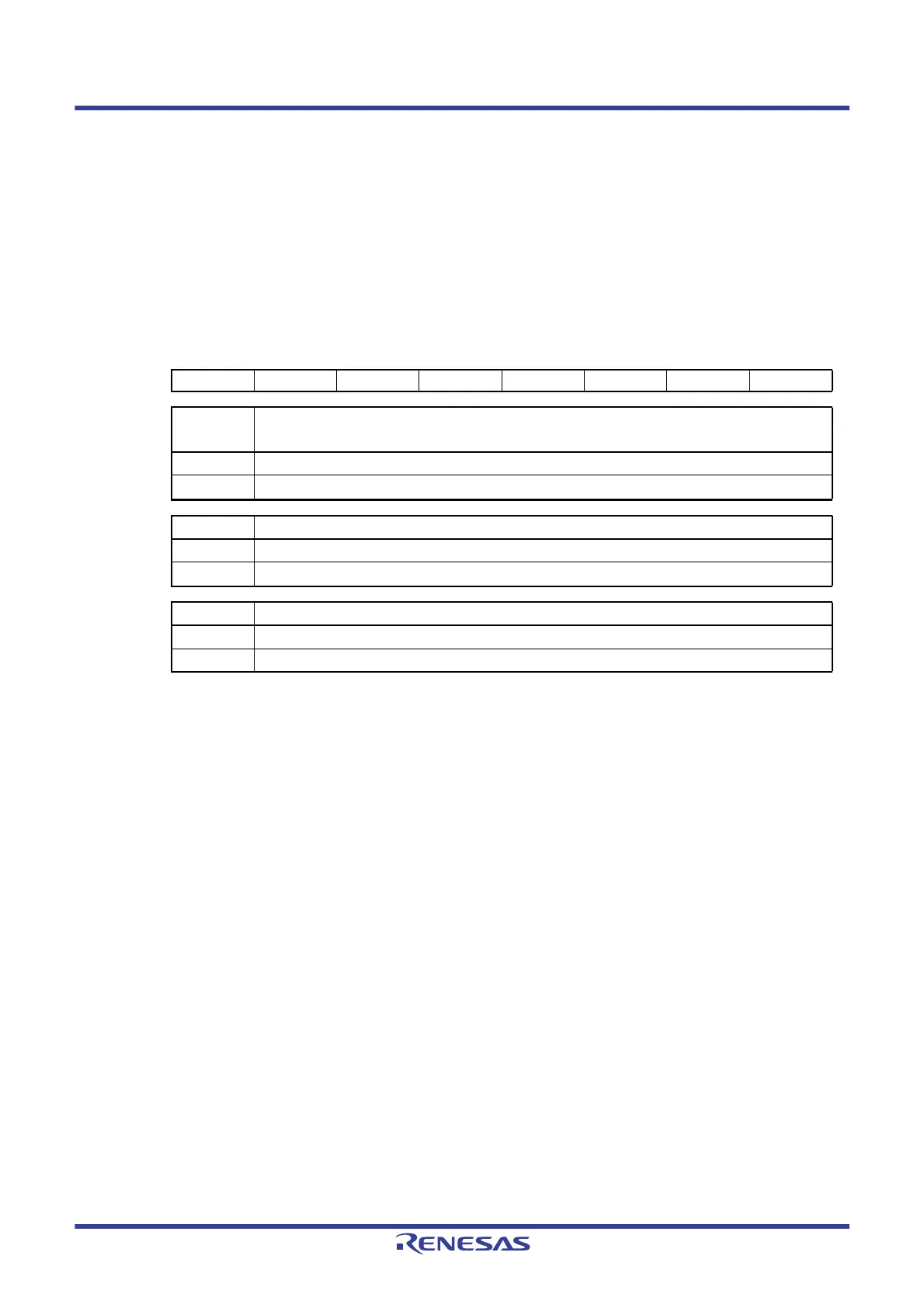

LVISEN

Note

3

Specification of whether to enable or disable rewriting the voltage detection level register (LVIS)

0 Disabling of rewriting the LVIS register (LVIOMSK = 0 (Mask of LVD output is invalid)

1

Enabling of rewriting the LVIS register

Note 3

(LVIOMSK = 1 (Mask of LVD output is valid)

LVIOMSK Mask status flag of LVD output

0 Mask of LVD output is invalid

1

Mask of LVD output is valid

Note 4

LVIF Voltage detection flag

0 Supply voltage (VDD) ≥ detection voltage (VLVD), or when LVD is off

1 Supply voltage (VDD) < detection voltage (VLVD)

Loading...

Loading...