RL78/G1H CHAPTER 7 TIMER ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 161 of 920

Dec 22, 2016

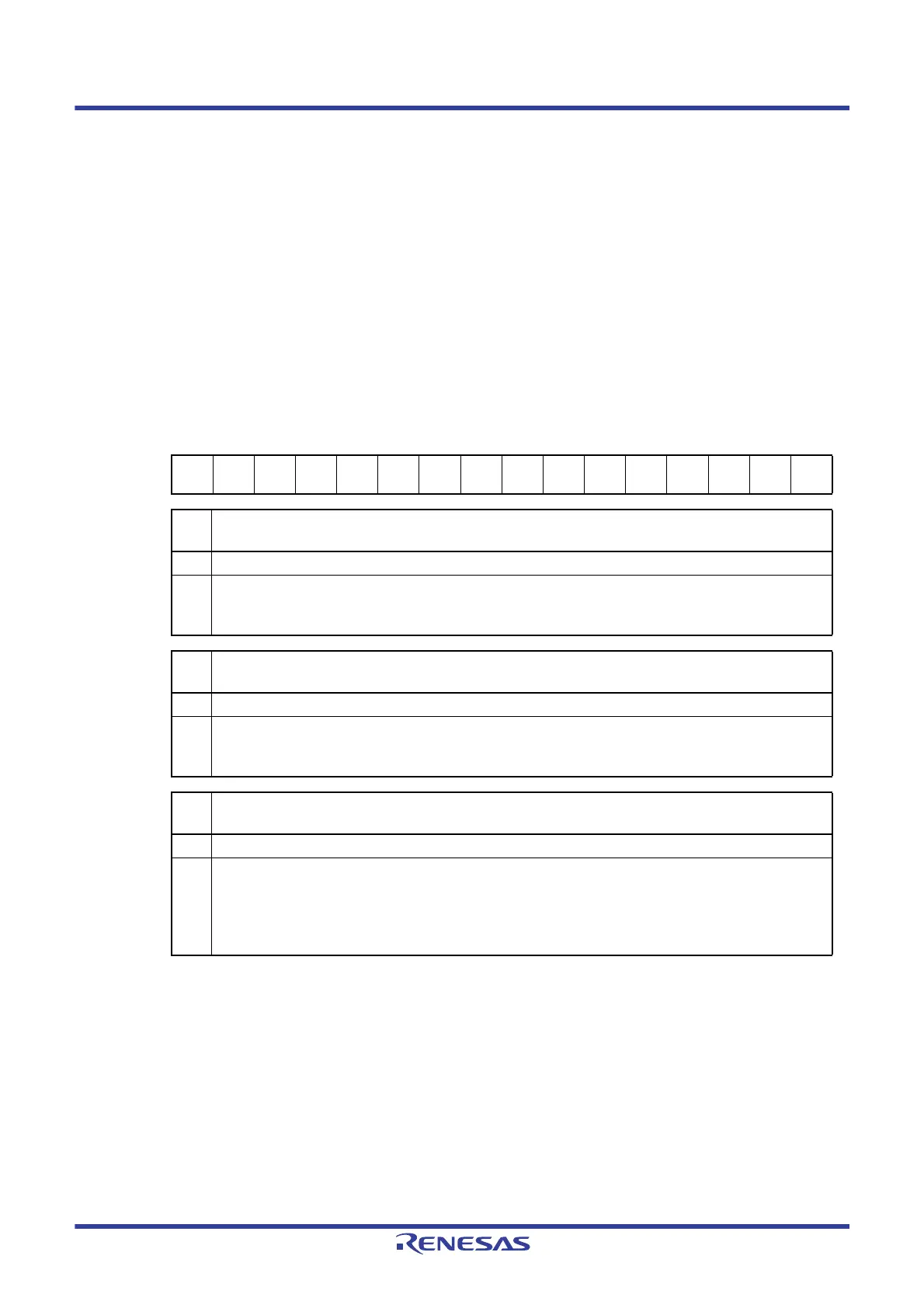

7.3.6 Timer channel start register m (TSm)

The TSm register is a trigger register that is used to initialize timer count register mn (TCRmn) and start the

counting operation of each channel.

When a bit of this register is set to 1, the corresponding bit of timer channel enable status register m (TEm) is set

to 1. The TSmn, TSHm1, TSHm3 bits are immediately cleared when operation is enabled (TEmn, TEHm1,

TEHm3 = 1), because they are trigger bits.

The TSm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the TSm register can be set with a 1-bit or 8-bit memory manipulation instruction with TSmL.

Reset signal generation clears this register to 0000H.

Figure 7 - 18 Format of Timer channel start register m (TSm)

(Cautions and Remarks are listed on the next page.)

Address: F01B2H, F01B3H (TS0) to F01F2H, F01F3H (TS1) After reset: 0000H R/W

Symbol1514131211109876543210

TSm0000

TSHm

3

0

TSHm

1

0 0 0 0 0 TSm3 TSm2 TSm1 TSm0

TSH

m3

Trigger to enable operation (start operation) of the higher 8-bit timer when channel 3 is in the 8-bit timer mode

0 No trigger operation

1 The TEHm3 bit is set to 1 and the count operation becomes enabled.

The TCRm3 register count operation start in the interval timer mode in the count operation enabled state (see

Table 7 - 4 in 7.5.2 Start timing of counter).

TSH

m1

Trigger to enable operation (start operation) of the higher 8-bit timer when channel 1 is in the 8-bit timer mode

0 No trigger operation

1 The TEHm1 bit is set to 1 and the count operation becomes enabled.

The TCRm1 register count operation start in the interval timer mode in the count operation enabled state (see

Table 7 - 4 in 7.5.2 Start timing of counter).

TSm

n

Operation enable (start) trigger of channel n

0 No trigger operation

1 The TEmn bit is set to 1 and the count operation becomes enabled.

The TCRmn register count operation start in the count operation enabled state varies depending on each

operation mode (see

Table 7 - 4 in 7.5.2 Start timing of counter).

This bit is the trigger to enable operation (start operation) of the lower 8-bit timer for TSm1 and TSm3 when

channel 1 or 3 is in the 8-bit timer mode.

Loading...

Loading...