RL78/G1H CHAPTER 8 TIMER RJ

R01UH0575EJ0120 Rev. 1.20 Page 229 of 920

Dec 22, 2016

8.3.4 Timer RJ control register 0 (TRJCR0)

The TRJCR0 register starts or stops count operation and indicates the status of timer RJ.

The TRJCR0 register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

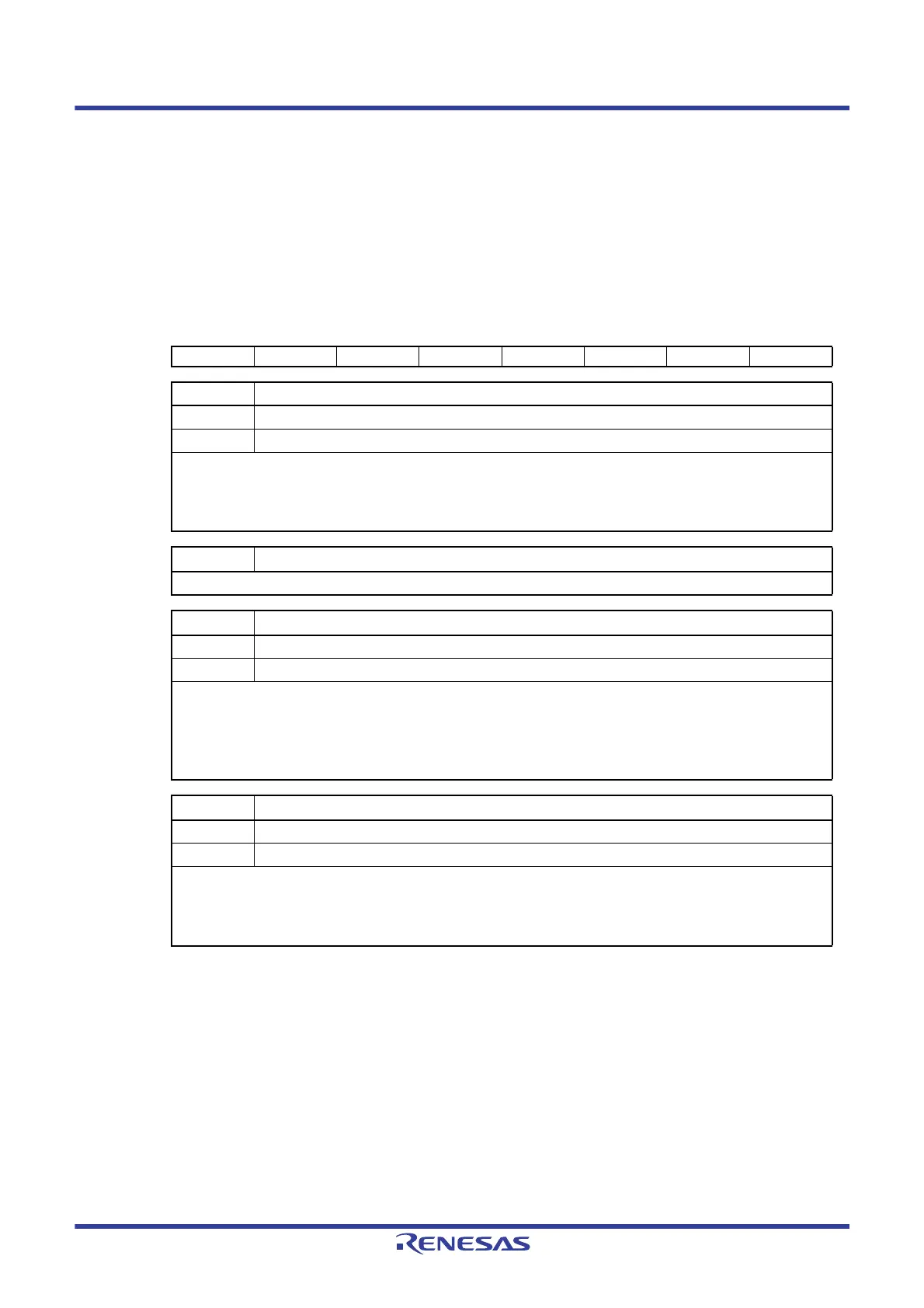

Figure 8 - 5 Format of Timer RJ control register 0 (TRJCR0)

Note 1. When 1 (count is forcibly stopped) is written to the TSTOP bit, bits TSTART and TCSTF are initialized at the

same time. The pulse output level is also initialized.

Note 2. For notes on using bits TSTART and TCSTF, see 8.5.1 Count Operation Start and Stop Control.

Address: F0240H After Reset: 00H R/W

Symbol76543210

TRJCR0 0 0 TUNDF 0 0 TSTOP TCSTF TSTART

TUNDF Timer RJ underflow flag

0 No underflow

1 Underflow

[Condition for setting to 0]

• When 0 is written to this bit by a program.

[Condition for setting to 1]

• When the counter underflows.

TSTOP

Timer RJ count forced stop

Note 1

When 1 is written to this bit, the count is forcibly stopped. The read value is 0.

TCSTF

Timer RJ count status flag

Note 2

0 Count stops

1 Count in progress

[Conditions for setting to 0]

• When 0 is written to the TSTART bit (the TCSTF bit is set to 0 in synchronization with the count source).

• When 1 is written to the TSTOP bit.

[Condition for setting to 1]

• When 1 is written to the TSTART bit (the TCSTF bit is set to 1 in synchronization with the count source).

TSTART

Timer RJ count start

Note 2

0 Count stops

1 Count starts

Count operation is started by writing 1 to the TSTART bit and stopped by writing 0. When the TSTART bit is set to 1

(count starts), the TCSTF bit is set to 1 (count in progress) in synchronization with the count source. Also, after 0 is

written to the TSTART bit, the TCSTF bit is set to 0 (count stops) in synchronization with the count source. For details,

see

8.5.1 Count Operation Start and Stop Control.

Loading...

Loading...