RL78/G1H CHAPTER 8 TIMER RJ

R01UH0575EJ0120 Rev. 1.20 Page 232 of 920

Dec 22, 2016

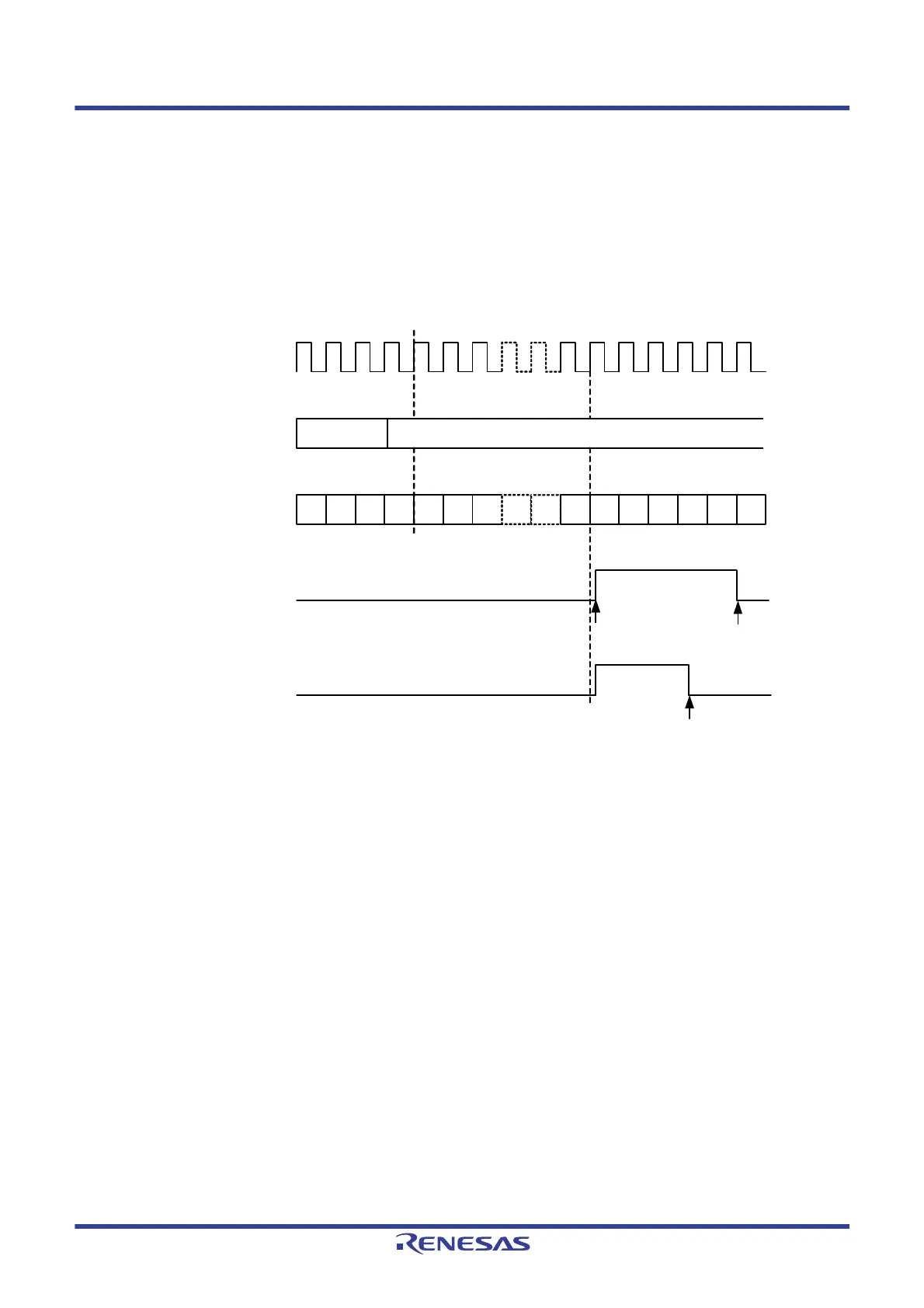

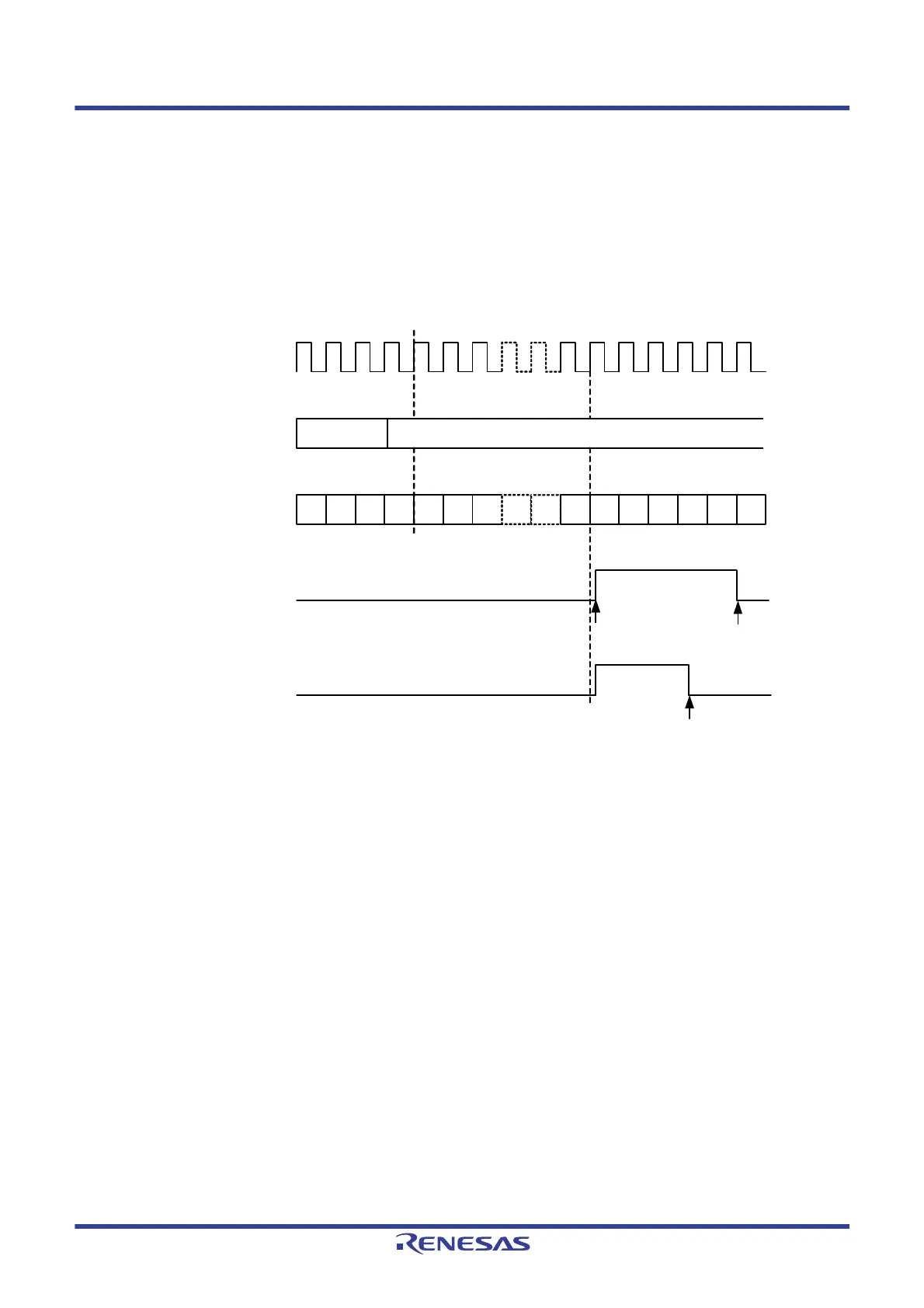

8.4.2 Timer Mode

In this mode, the counter is decremented by the count source selected by bits TCK0 to TCK2 in the TRJMR0

register.

In timer mode, the count value is decremented by 1 each time the count source is input. When the count value

reaches 0000H and the next count source is input, an underflow occurs and an interrupt request is generated.

Figure 8 - 8 shows the Operation Example in Timer Mode.

Figure 8 - 8 Operation Example in Timer Mode

Timer RJ0 counter

Counter reloading occurs

Set to 0 by a

program

Count source

Reload register

TUNDF bit in

TRJCR0 register

02FAH02F9H02F8H02F7H 1010H 100FH 100EH ••••• ••••• 0000H 1010H 100FH100EH100DH100CH100BH

Previous value

(0300H)

New value (1010H)

Acknowledgement of an interrupt request

IF bit in INTTRJ0 register

An underflow

occurs

Loading...

Loading...