RL78/G1H CHAPTER 15 SERIAL INTERFACE IICA

R01UH0575EJ0120 Rev. 1.20 Page 453 of 920

Dec 22, 2016

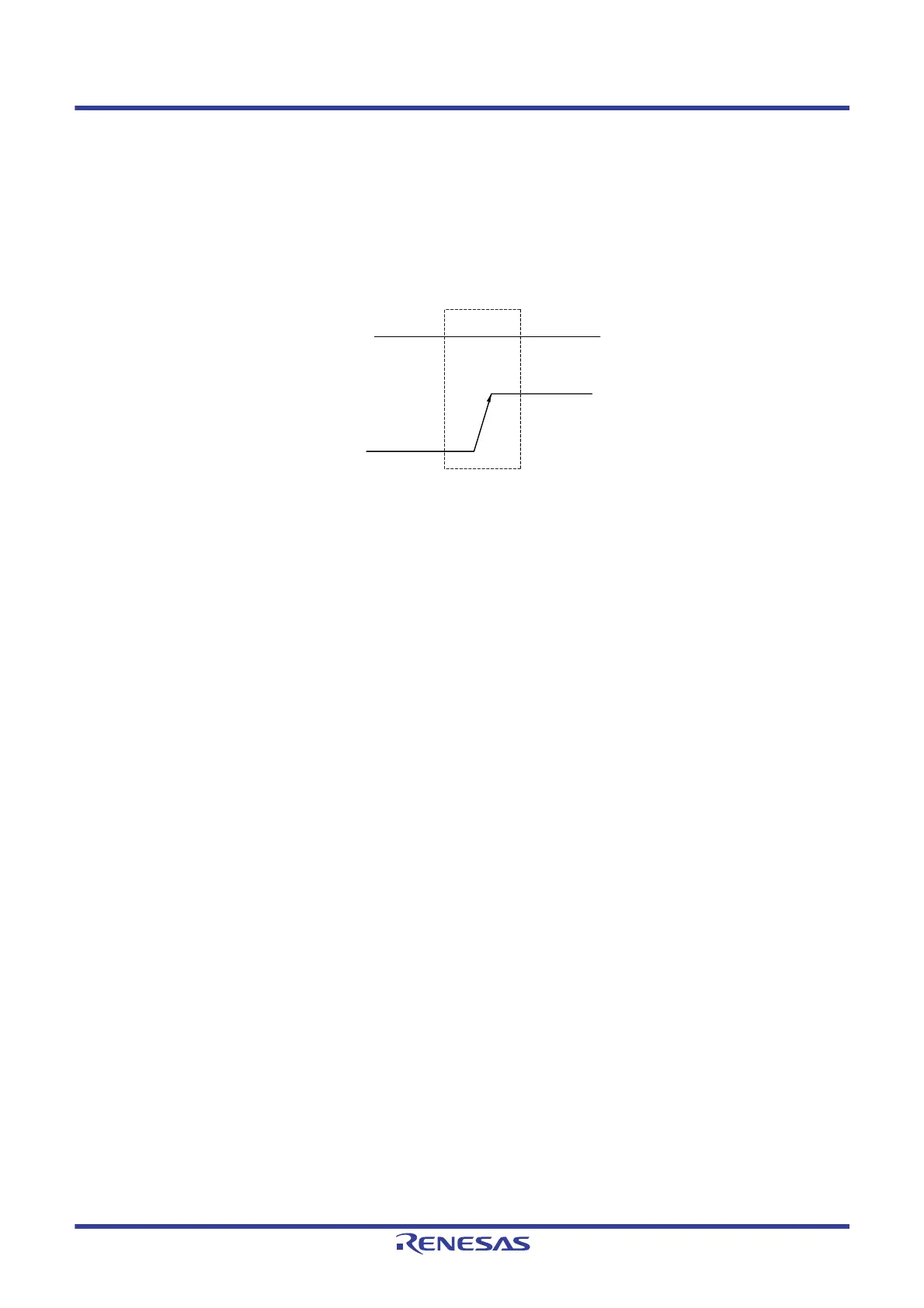

15.5.5 Stop condition

When the SCLAn pin is at high level, changing the SDAAn pin from low level to high level generates a stop

condition.

A stop condition is a signal that the master device generates to the slave device when serial transfer has been

completed. When the device is used as a slave, stop conditions can be detected.

Figure 15 - 24 Stop Condition

A stop condition is generated when bit 0 (SPTn) of IICA control register n0 (IICCTLn0) is set to 1. When the stop

condition is detected, bit 0 (SPDn) of the IICA status register n (IICSn) is set to 1 and INTIICAn is generated

when bit 4 (SPIEn) of the IICCTLn0 register is set to 1.

Remark n = 0, 1

Loading...

Loading...