RL78/G1H CHAPTER 14 SERIAL ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 341 of 920

Dec 22, 2016

14.3.7 Serial status register mn (SSRmn)

The SSRmn register is a register that indicates the communication status and error occurrence status of channel

n. The errors indicated by this register are a framing error, parity error, and overrun error.

The SSRmn register can be read by a 16-bit memory manipulation instruction.

The lower 8 bits of the SSRmn register can be set with an 8-bit memory manipulation instruction with SSRmnL.

Reset signal generation clears the SSRmn register to 0000H.

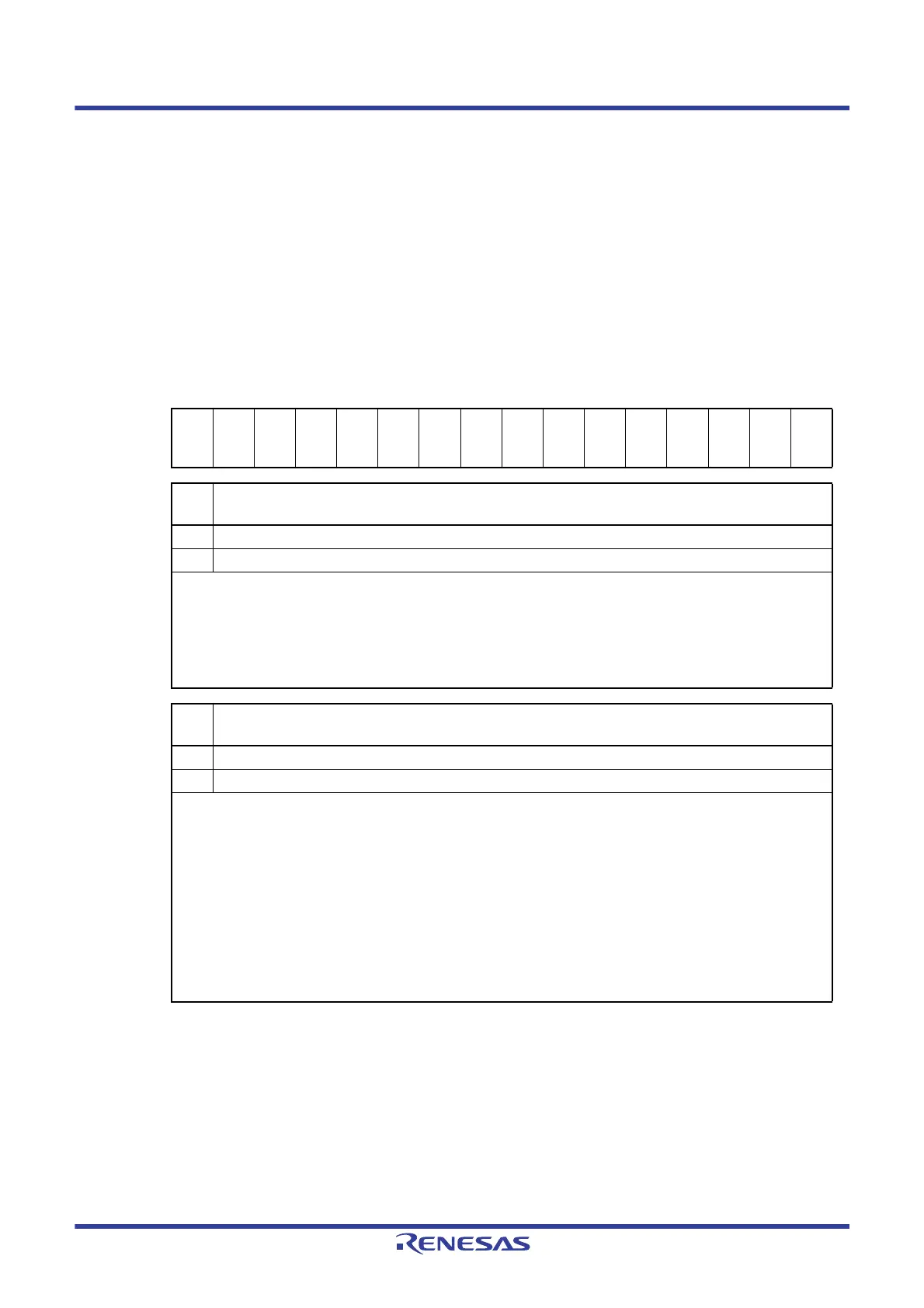

Figure 14 - 12 Format of Serial status register mn (SSRmn) (1/2)

Note The SSR03 and SSR13 registers only.

Address: F0104H, F0105H (SSR02), F0106H, F0107H (SSR03), After reset: 0000H R

F0140H, F0141H (SSR10) to F0146H, F0147H (SSR13)

Symbol1514131211109876543210

SSRmn000000000

TSF

mn

BFF

mn

00

FEF

mn

Note

PEF

mn

OVF

mn

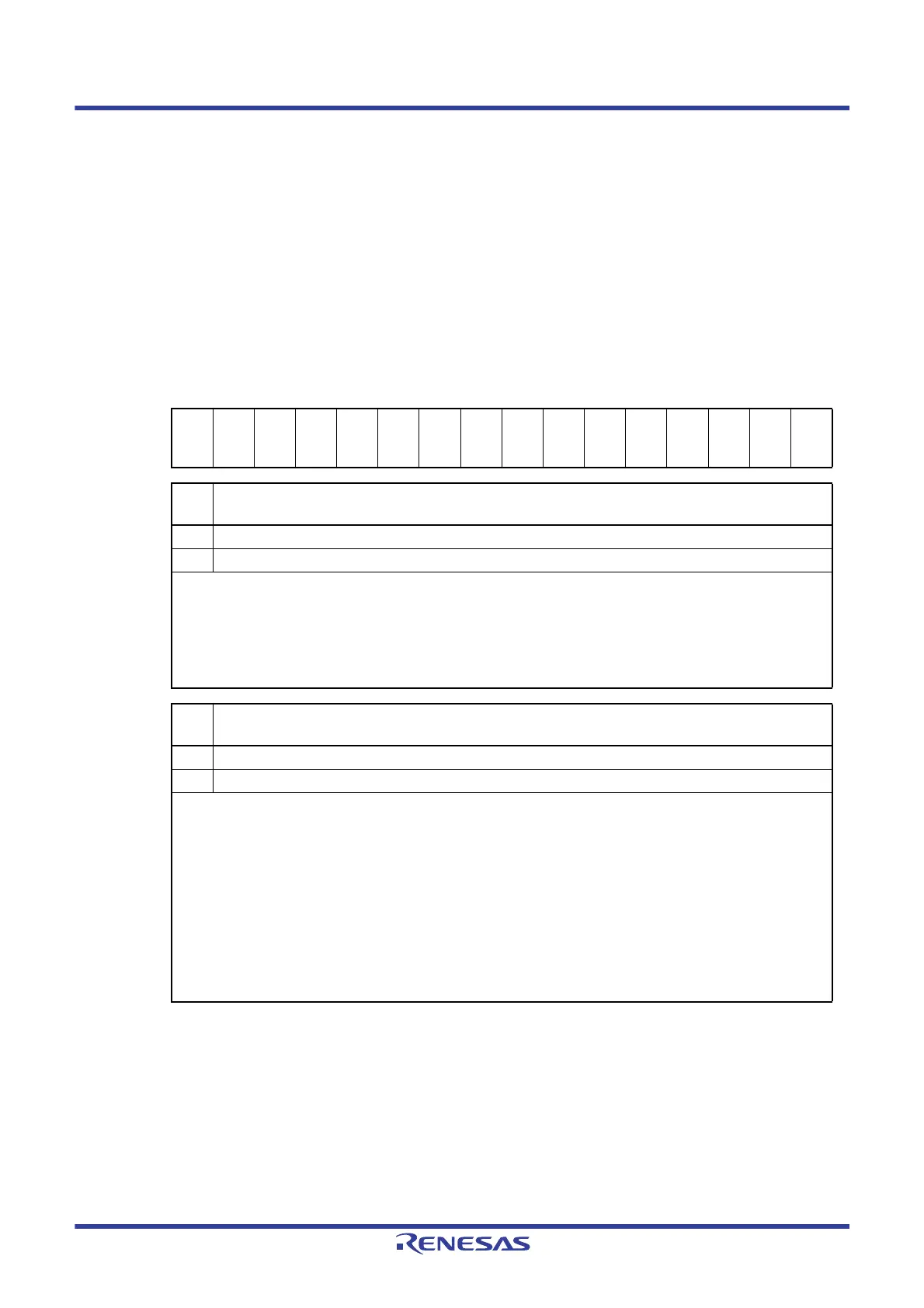

TSF

mn

Communication status indication flag of channel n

0 Communication is stopped or suspended.

1 Communication is in progress.

<Clear conditions>

• The STmn bit of the STm register is set to 1 (communication is stopped) or the SSmn bit of the SSm register is set to

1 (communication is suspended).

• Communication ends.

<Set condition>

• Communication starts.

BFF

mn

Buffer register status indication flag of channel n

0 Valid data is not stored in the SDRmn register.

1 Valid data is stored in the SDRmn register.

<Clear conditions>

• Transferring transmit data from the SDRmn register to the shift register ends during transmission.

• Reading receive data from the SDRmn register ends during reception.

• The STmn bit of the STm register is set to 1 (communication is stopped) or the SSmn bit of the SSm register is set to

1 (communication is enabled).

<Set conditions>

• Transmit data is written to the SDRmn register while the TXEmn bit of the SCRmn register is set to 1 (transmission or

transmission and reception mode in each communication mode).

• Receive data is stored in the SDRmn register while the RXEmn bit of the SCRmn register is set to 1 (reception or

transmission and reception mode in each communication mode).

• A reception error occurs.

Loading...

Loading...